#### Instituto Tecnológico y de Estudios Superiores de Monterrey

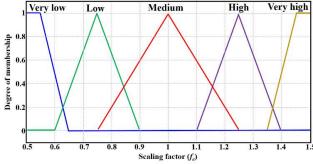

Campus Monterrey

#### School of Engineering and Sciences

## Modeling and control of emerging DC-DC topologies for renewable energy applications

A dissertation presented by

#### Carlos Alberto Villarreal Hernández

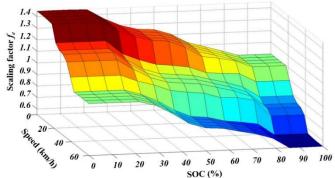

Submitted to the School of Engineering and Sciences in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in

**Engineering Science**

Major in Power Electronics

## Dedication

To my lovely family, who has always been there for me.

My parents Rosa and Javier.

My sister Alexandrina and her husband Joaquin.

To Leonardo and Valentina.

### Acknowledgements

I would like to thank the Tecnológico de Monterrey for granting me a scholarship during my PhD studies, a special mention to the School of Engineering and Sciences and their support to the Power Electronics laboratory, in which I achieved all my projects presented in this dissertation.

I would like to thank to CONACyT for giving me the support grant along my PhD studies and the additional support to the SENER-CONACyT program "Laboratorio binacional para la gestión inteligente de la sustentabilidad energética y formación tecnológica" during my international research in Arizona State University.

I express my gratitude to my advisor Dr. Jonathan C. Mayo Maldonado, who has always been there with his guiding and support for me over the years. I would like to thank him for all the advice, motivation and knowledge he transmitted me over these years.

I would like to express my gratitude to my co-Advisor Dr. Jesus Valdez Resendiz for all his advice and guidance over these years. My sincere thanks to my commite members, Dr. Gerardo Escobar Valderrama and Dr. Daniel Guillen Aparicio, your discussion, feedback, and new ideas helped me to always be trying to improve myself.

My sincere thanks to Dr. Osvaldo M. Micheloud, for all the support and facilities that he brought to the Power Electronics laboratory.

Javier Loranca, Juan Percino and David Rivera, my colleagues, who shared with me this PhD experience, I would like to thank you for all the adventures, fun and knowledge. Thanks for all your help and contributions.

Finally, I would like to thank all my friends in Monterrey.

## Modeling and control of emerging DC-DC topologies for renewable energy applications

by Carlos Alberto Villarreal Hernández

#### **Abstract**

Renewable energy is attracting investigation and investment worldwide. This can be notice by studying cases of countries such as, Germany, China or Sweden, which are making big investment in this field, brief information about these and other European countries that are in the top ten of the renewable energy generation are presented.

The main topic in this dissertation is the penetration of renewable energy into the grid, since it has been increasing considerably over the years. In this topic, it is involve the study of DC-DC and DC-AC power conversion. In this dissertation the DC-DC power conversion stage is studied in detail. Conventional DC-DC topologies are used in the industry in this DC-DC power conversion stage, however, these topologies have some limitations. For that reason, new topologies have been emerging, their characteristics represent an improvement over the limitations of conventional DC-DC topologies. Considering that, in this dissertation some of the emerging topologies, their modeling and control are studied. Moreover, it will be discuss how the interconnection of the renewable energy source is usually made, and how a stepping-up converter is incorporated into the system, and what are the main characteristics of this converter in order to have proper exploitation of the source. Also, it is considered that renewable energy sources are intermittent sources, which is undesirable since it may imply interruptions to the electrical supply, to overcome this issue, a set of controllers are proposed. Finally, not only the theoretical aspects are discussed, but also the hardware implications. A brief explanation of the chapters included in this dissertation is presented next:

In Chapter 2 a novel control technique "Minimum Current-Ripple Point Tracking" is presented, which is an output current/voltage control for interleaved DC-DC converters with dual switched input-inductors, i.e., interleaved input inductors controlled by independent switches. The controller for the interleaved converter encompasses three control stages: current stabilization, output-voltage regulation and minimum input-current-ripple control. In contrast with the two first loops, the latter is a novel stage introduced in this work to allow operation with minimum input-current-ripple in the whole operating region. That is, even though the converter has been designed for operation with minimum ripple in a given operating point, the scheme is able to dynamically deviate from this point to a new one where the ripple is minimized and the output voltage remains constant.

In Chapter 3 it is shown how this new MCRPT control strategy is applicable to the study of double dual boost converters, in which discrete-time linear and non-linear controllers are presented. Under the proposed linear control technique, a new stability condition and gain

tuning methodology are presented. Moreover, a nonlinear discrete-time controller is proposed in case of requiring performance optimization over a wider signal range.

In Chapter 4, the MCRPT control strategy is tested in a Proton-Exchange Membrane Fuel Cell (PEMFC) . A discrete-time controller is selected for this purpose. In this way, the converter can mitigate the harmonic distortion on the current extracted from the PEMFC, which is beneficial to improve the efficiency and lifetime of the cell.

In Chapter 5 the MCRPT control technique is combine with a nonlinear controller.

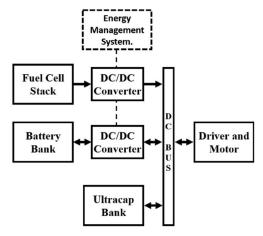

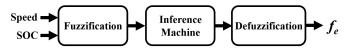

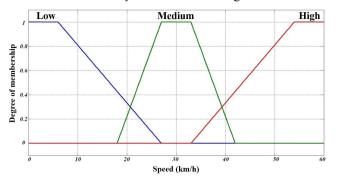

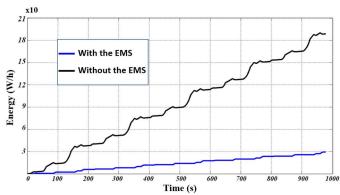

In Chapter 6 a strategy to regulate the charge and discharge of ultracapacitors in electric vehicles applications is explained.

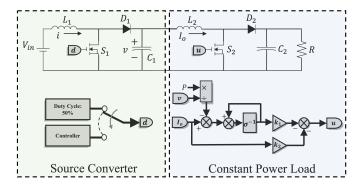

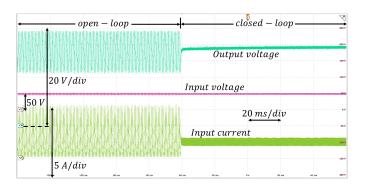

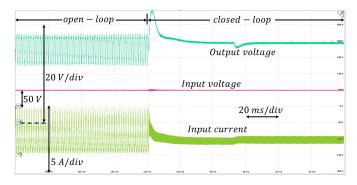

In Chapter 7 a controller that is able to stabilize DC-DC converters feeding a constant load is studied.

Chapter 8 explains in detail the modeling of a DC-DC, this converter has the necessary characteristics for renewable energy. Finally, in Chapter 9 the conclusions of this dissertation are presented. The proposed controllers for the DC-DC converters are validated with experimental results, in which scale prototypes were designed.

## **Contents**

| Al | bstract                                                                                                                                        | ix                     |

|----|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 1  | Introduction1.1 Motivation1.2 Problem Statement and Context1.3 Objectives1.4 Solution overview                                                 | 1<br>2<br>4<br>7<br>7  |

| 2  | Minimum Current-Ripple Point Tracking Control for Interleaved Dual Switched-Inductor DC-DC Converters                                          | -<br>13                |

| 3  | Discrete-time Modeling and Control of Double Dual Boost Converters with Implicit Current-Ripple Cancellation over a Wide Range Operating Range | 27                     |

| 4  | A Double Dual Boost Converter with Switching Ripple Cancellation for PEMFC Systems                                                             | 41                     |

| 5  | Minimum Current-Ripple Point Tracking for Renewable Energy Applications                                                                        | 61                     |

| 6  | Energy Management Strategy for Ultracapacitors in Hybrid Electric Vehicles                                                                     | 71                     |

| 7  | <b>Energy-based Stabilizing Controllers for DC-DC Converters Feeding Constant Power Loads</b>                                                  | 81                     |

| 8  | Modeling and Control of an Interleaved DC-DC Multilevel Boost Converter                                                                        | 91                     |

| 9  | Conclusions 9.1 Contributions                                                                                                                  | <b>99</b><br>99<br>100 |

## **Chapter 1**

## Introduction

High-power converters started with gate-turn-off (GTO) thyristors with the commercial development of 4500 volts switching devices. These GTO devices became the standard until the development of the high-power insulated-gate bipolar transistors (IGBTs) and gate-commutated thyristors (GCTs) in the 1990s. These switching devices have improved switching characteristics, like reduced power losses, ease of gate control, and snubberless operation, which make them optimal for high-power applications [1]. Out of the development in the high-power switches, power electronics is an area in constant development, nowadays it is involved in many applications, such as automotive, illumination, battery backup systems, renewable energy sources and many others.

In this dissertation, the DC-DC converter, which is a power electronics component, are studied, and how it improves the penetration of renewable energy into the grid. These DC-DC converters are a part of the hybrid inverter, the latest is usually incorporated to have a proper interconnection between the renewable energy source and the grid. A lot of topologies of DC-DC converters are available in the literature, depending on the application, each topology has advantages over the others. Considering that the application of the hybrid inverter previously mentioned is for renewable energy, their main characteristics needs to be considered.

Firstly, it is common that renewable energy is generated at low voltages, which makes it inconvenient to have a direct connection with the grid. Then a DC-DC topology with the ability to increase the input voltage is required. For this reason, some DC-DC converters have been proposed to step-up voltages in an efficient and reliable way [4–6]. Among the desirable features of such converters are the use of moderate duty cycles to maintain high-efficiency.

Added to this, this step-up stage has an inherent characteristic associated, which is the input current ripple [2,3]. This ripple is undesirable, since it represents a low efficiency and a decay in the lifetime of some sources. Renewable DC sources such as fuel cells and solar panels are between the sources that produce low output voltages and are affected by this input current ripple.

Secondly, renewable energy such as solar or wind has a fluctuating output voltage, due to their own nature, for this, the converter must be incorporated with a control stage. The principal objective of this controller is to maintain a constant output voltage under disturbances of the system, either if it is a input voltage (as a consequence of renewable energy variations) or a load variation (as a consequence of the demand that the system may have). In this dissertation

the control design considers that a fixed operation point is required, but also a system with a wide operating range is studied.

Common solutions for these inconvenient features of renewable energy are commercially available, nevertheless, the use of conventional topologies is highly extended. The inconvenient with these conventional topologies is that they deliver a restricted output voltage, that is, they have limited gain. Moreover, the input current ripple cancellation is also limitated to a specific point, which is a disadvantage considering that renewable energy sources are not constant. For these reasons, in this dissertation, instead of conventional topologies, emerging topologies for renewable energy applications are considered. These emerging topologies have some advantages over the conventional, like a higher gain and a better ripple cancellations characteristics. The use of these emerging topologies imply some challenges, like their modeling and control. For this, in this dissertation, a proper modeling technique and a adequate control strategy are proposed.

#### 1.1 Motivation

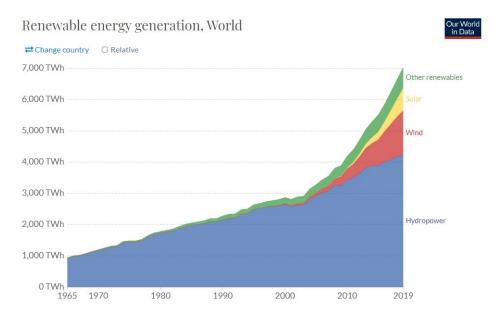

Since 2000, the production of renewable energy has been increasing over the years worldwide, as can be appreciated in Fig. 1.1, these data was obtained from [7]. In this graph it can be appreciated how the wind and solar energy production are becoming relevant. Nevertheless, hydropower is by far the most common renewable energy source.

Figure 1.1: Renewable energy generation worldwide.

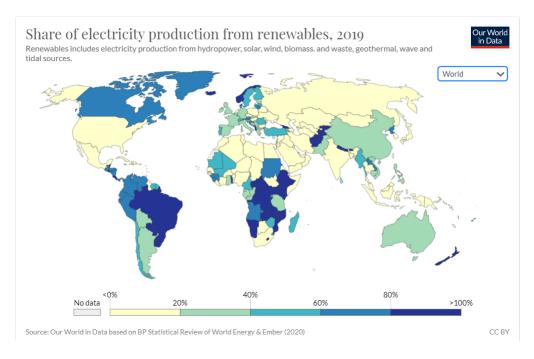

To have a better understanding on the distribution of this renewable energy production, Fig. 1.2 is shown, in this figure a world map where each country is colored according to the amount of renewable energy production is shown. It can be appreciated how the blue countries are between the most contributors to this matter. Most of the blue colored countries are due to

1.1. MOTIVATION 3

the hydraulic reserves they have. But other countries colored in green, such as some European countries, are increasing their solar and wind energy production, i.e. Germany or Sweden.

Figure 1.2: Share of electricity production from renewable energy worldwide.

A constant increase in the global consumption of energy must be a concern for all countries all over the world. Some countries have a better progress in this matter like it was appreciated in Fig. 1.2. This environmental compromise is recorded by the Energy Trilemma Index, a document that the World Energy Council updates every year. In 2016 the three first places were: Denmark, Switzerland and Sweden, respectively, while Mexico was in the 52 place [8]. In the year of realization of this dissertation (2020), the top ten of the rank is still dominated by OECD countries, whit the top three as follows: Switzerland, Sweden, Denmark, while Mexico is in the 45 place. The top ten of this ranking is dominated by European countries, this top ten rank illustrates the benefit of longstanding active energy policies [8].

It can be appreciated how the European countries become the leaders in renewable energies, particularly from wind generation. From this top three, it can be appreciated the case of Denmark, which is a great example of how the fossil fuels can be replaced by renewable energy sources. Denmark is a leader in generation of power from wind, it is far away from his nearest rival, which is Ireland, the latest have 28% of its power from wind generation, while Denmark recorded a 47% of power generated by wind [9]. It is surprising how these European countries from the top of renewable energy generation accomplished their goals, that is the case of Sweden, which is a country in constant growing with the objective of 100% of renewable energy production by the year of 2040, which may be seem so ambitious, but considering that in 2012, Sweden reached the government's objective of 50% [10], it seems to be plausible.

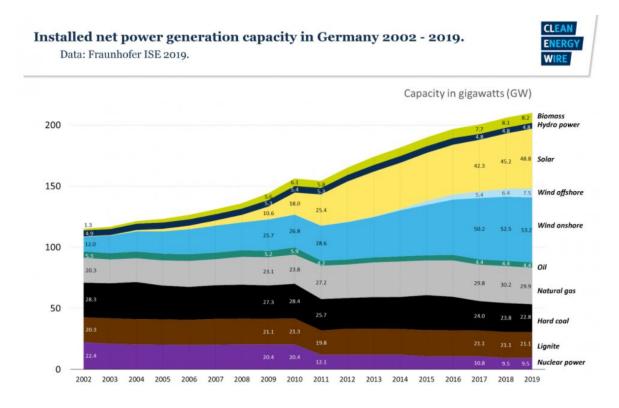

But renewable energy can also be obtained from the sun. A remarkable example on solar energy is Germany, which is also in the top ten of the Energy Trilemma Index, as can be

appreciated in the Fig. 1.3, which was obtained from [11], most of the installed capacity are solar and wind energy.

Figure 1.3: Installed net power generation capacity in Germany 2002-2019.

It is possible to continue remarking the best countries in renewable energy exploitation, but it is clear that clean energy is the global tendency around the world. Or eventually will be for some countries that are not still compromise with the environment.

#### 1.2 Problem Statement and Context

We have seen how the energy industry is making big changes due to new technologies and new environmental concerns, this implies new challenges to the electrical industry. The incorporation of these new technologies into the existing electrical system is the main objective of recent studies.

While studying renewable energy sources incorporation to the grid, the power transfer is one of the main objects of study. This is, how to improve the efficiency of the system to exploit the maximum power from the source. As was previously discussed, renewable energy sources have some inherent characteristics that limits their exploitation; one of these is the low voltage that these sources produces, to solve this issue, extra components need to be included in the system, the most common solution for this, is the use of power transformers. Nevertheless, in the area of power electronics, analogous devices to power transformers are

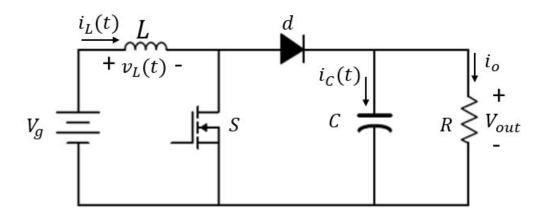

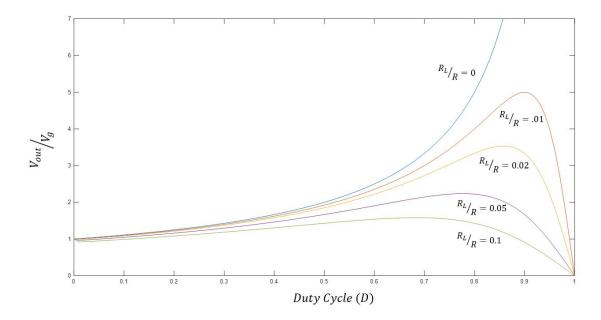

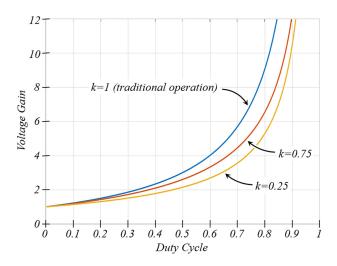

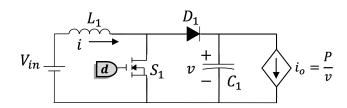

object of study, namely the power converters. One of the main advantages over the classical power transformers, is the possibility to convert direct current to direct current (DC-DC). A variety of power converters are available, this variation is a result of how the components are connected to form each topology. Since our primary objective is to increase the voltage of the source, topologies with this ability are desired. The basic step-up converter is the well-known boost converter, shown in Fig. 1.4. Nevertheless, as shown in Fig. 1.5 [2] the output voltage of this boost converter, which can be referred as a conventional topology, is limited. As the output voltage of the converter increases (i.e. the duty cycle of the converter reaches value of 1) the gain  $(V_{out}/V_g)$  tends to zero. Then, a proper topology, with the basic principle of stepping-up the voltage as the boost topology does, but with a higher gain at the same duty cycle, in order to avoid extreme duty cycles, needs to be selected to overcome the low voltage of the renewable energy source.

Figure 1.4: Boost converter.

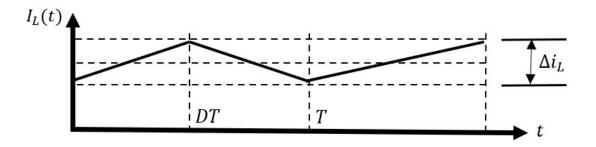

In addition to the low output voltage of conventional topologies, the input current ripple of these topologies tends to be unacceptable to have a proper utilization of the energy available from the power source. A typical waveform of this ripple is shown in Fig. 1.6 [2]. In this figure the input current ripple expected from a conventional boost topology is assigned as  $\Delta i_L$ . As previously said, this ripple is undesirable because it represents the wasted energy from the source, also it affects the efficiency and lifetime of some renewable energy sources, such as solar panels or fuel cells. This decrees in efficiency of solar panels was recorded in [12], the result can be appreciated in Table 1.1, where an open loop experiment was carried out and Table 1.2, where the results of a closed loop are shown. The input current ripple cancellation is a common topic in the literature, some of this literature use the conventional topology in combination with extra components, like passive filters or coupled inductors. In this dissertation non conventional topologies are selected to overcome this input current ripple cancellation.

The use of new topologies imply new challenges, like their modeling. The modeling of conventional topologies is well documented. Averaging is a recurrent modeling technique

Figure 1.5: Output voltage vs duty cycle in a boost converter.

with a lot of advantages to avoid dealing with differential equations. Nevertheless, this technique is not applicable in some cases, for example when capacitors are in parallel connection. These parallel capacitors are essential in DC-DC converters with multiplier stages. Then new modeling techniques need to be performed.

As was previously discussed, the DC-DC converter must have a proper control to deal with intermittences to the system, while maintaining constant output voltage. Since some of the step-up converters are a result of the main principle of the conventional boost topology, they share a non-minimum phase characteristic with respect to the output voltage, that is, the transfer function has a zero in the right half plane. This characteristic limits their control bandwidth, to deal with this non-minimum phase, a proper controller needs to be selected.

Figure 1.6: Input-current ripple of a boost converter.

In this dissertation these drawbacks of renewable energy sources are solved, first by

1.3. OBJECTIVES 7

| C                           | Open loop |      |  |  |  |

|-----------------------------|-----------|------|--|--|--|

| % Isc P <sub>avg</sub> % et |           |      |  |  |  |

| 5                           | 133.3     | 98   |  |  |  |

| 10                          | 127.7     | 93.9 |  |  |  |

| 20                          | 118.1     | 86.8 |  |  |  |

| 30                          | 109.5     | 80.5 |  |  |  |

| 40                          | 102.8     | 75.6 |  |  |  |

| 50                          | 97.6      | 71.8 |  |  |  |

| 60                          | 92.8      | 68.3 |  |  |  |

| 70                          | 89.1      | 65.4 |  |  |  |

| 80                          | 81.9      | 60.2 |  |  |  |

| 90                          | 77.6      | 57.1 |  |  |  |

| C     | Closed loop |       |  |  |  |

|-------|-------------|-------|--|--|--|

| % Isc | $P_{avg}$   | % eff |  |  |  |

| 5     | 132.3       | 97.3  |  |  |  |

| 10    | 129.9       | 95.5  |  |  |  |

| 20    | 127.6       | 93.8  |  |  |  |

| 30    | 122.2       | 89.8  |  |  |  |

| 40    | 116.2       | 85.5  |  |  |  |

| 50    | 110.3       | 81.1  |  |  |  |

| 60    | 103.3       | 76.0  |  |  |  |

| 70    | 96.7        | 71.1  |  |  |  |

| 80    | 74.7        | 54.9  |  |  |  |

| 90    | 41.4        | 30.4  |  |  |  |

Table 1.1: Relation between input ripple current and the solar panel efficiency.

Table 1.2: Relation between input ripple current and the solar panel efficiency.

selecting a topology that is capable of producing a greater output voltage than conventional topologies, and second, the input current ripple is minimized, in this way the lifetime and efficiency of the renewable energy source are improve. Added to these improvements, in this dissertation, the control of the power converter is designed in such way that even when some of the renewable energy sources are intermittent, the power transfer is able to be in a continuous form.

#### 1.3 Objectives

The objectives of this work can be summarized as follows:

- Develop modeling techniques applicable to emerging DC-DC topologies.

- Study and develop control strategies considering the necessities of renewable energy.

- Develop new control tuning techniques applicable to the topologies used in this dissertation.

- Propose and develop a ripple cancellation technique according to the topologies used in this dissertation.

- Develop the ability to test and corroborate theoretical results via hardware implementation.

- Prove that the proposed techniques are useful in real renewable energy applications.

#### 1.4 Solution overview

The main challenges of renewable energy sources and their implications on the DC-DC topology were discussed in previous sections. The necessity for high gain, the input current ripple

cancellation, new modeling strategies, and a proper control are the primary objectives of this dissertation.

Instead of using the conventional boost topology, along this document, two emerging topologies with the desired ccharacteristics for a proper exploitation of renewable energy, will be discuss; firstly, a topology named "Interleaved Multilevel Boost Converter", and secondly, a topology named "Double Dual Boost Converter"; these two topologies selected, have in common a high gain property, and a input current ripple cancellation capability. For the modeling of these topologies, along this dissertation a continuous mode of operation is considered, that is, the current of the converter is greater than zero all the time. An important contribution for the modeling of these emerging topologies, is that they were analyzed in such way, that even when the number of components in the converter increases with respect to conventional topologies, the resultant model is quite similar in complexity. The control for these topologies was designed considering the non-minimum phase characteristics previously discussed, then a minimum-phase variable was selected to implement the control, that is, the input current of the converters, nevertheless, since the variable to be controlled is the output voltage, then an external control loop is added to the first current control loop, in that way, the converter is stable and the output voltage remains constant.

Since all of the proposed techniques of this dissertation needs to be implemented, the discrete-time modeling of these topologies is studied. In this dissertation, an approximate discrete-time model is proposed, in which a nonlinear set of equations are employed. This modeling allows the use of a nonlinear controller, that is also exposed.

Along this document, some publications are presented. Each of these publications deals with a specific issue previously described.

- In Chapter 2, the "Interleaved Multilevel Boost Converter" is presented, its modeling strategy is discussed, and the topology is combined with a new control strategy, that ensures an active minimization in the input current ripple.

- In Chapter 3, a linear and a nonlinear discrete-time controllers are presented. In this article an approximate discretization process is presented. Also, a new stabilizing condition is discussed as a new tuning control technique. These two contributions are demonstrated on a "Double Dual Boost Converter", which is an emerging topology with a ripple cancellation capability, reason why an implicit current ripple cancellation technique is considered.

- In Chapter 4, the input current ripple cancellation control strategy presented in Chapter 1 is tested under the operation of a fuel cell, moreover, the control strategy is performed in discrete-time. The main objective of this article, is to proved how the technique improves the extraction of energy from a fuel cell. That is, the proposed techniques are applicable to real renewable energy sources.

- In Chapter 5 the ripple technique presented in Chapter 1, is combined with a nonlinear controller, proving that it is possible to combine this technique with another type of controllers.

9

- In Chapter 6 a strategy to manage the energy available in electric vehicles is presented. Due to the penetration of hybrid electric vehicle in the electrical system, it is an important topic to deal with.

- In Chapter 7, the study of DC-DC converters feeding constant power loads is presented.

- In Chapter 8, the modeling of the "Interleaved Multilevel Boost Converter" is discussed in detail and the control, of this topology, which is a topology with proper characteristics for interconnection of renewable energy sources, is presented.

## **Bibliography**

- [1] B. Wu, High-Power Converters and AC Drives. Wiley, 2007.

- [2] R. W. Erickson and D. Maksimovic, *Fundamentals of Power Electronics*. Springer, 2ed ed., 2001.

- [3] L. Bellinaso, H. Figueira, M. Basquera, R. Vieira, H. Gründling, and L. Michels, "Cascade control with adaptive voltage controller applied to photovoltaic boost converters," *IEEE Trans. Ind Appl.*, vol. 55, pp. 1903–1912, March 2019.

- [4] M. Lakshmi and S. Hemamalini, "Nonisolated high gain dc-dc converter for dc microgrids," *IEEE Transactions on Industrial Electronics*, vol. 65, pp. 1205–1212, Feb 2018.

- [5] R. H. Ashique and Z. Salam, "A high-gain, high-efficiency nonisolated bidirectional dc-dc converter with sustained zvs operation," *IEEE Transactions on Industrial Electronics*, vol. 65, pp. 7829–7840, Oct 2018.

- [6] M. R. Banaei and S. G. Sani, "Analysis and implementation of a new sepic-based single-switch buck-boost dc-dc converter with continuous input current," *IEEE Transactions on Power Electronics*, vol. 33, pp. 10317–10325, Dec 2018.

- [7] H. Ritchie and M. Roser, "Renewable energy." urlhttps://ourworldindata.org/renewable-energy, 2020.

- [8] W. E. Council, "Energy trilemma index." urlhttps://trilemma.worldenergy.org/, 2020.

- [9] J. Gronholt-Pedersen, "Denmark sources record 47% of power from wind in 2019." urlhttps://www.reuters.com/article/us-climate-change-denmark-windpower-idUSKBN1Z10KE, 2020.

- [10] Sweden.se, "Energy use in sweden." urlhttps://sweden.se/nature/energy-use-in-sweden/: :text=Sweden2020.

- [11] K. Appunn, Y. Haas, and J. Wettengel, "Germany's energy consumption and power mix in charts." urlhttps://www.cleanenergywire.org/factsheets/germanys-energy-consumption-and-power-mix-charts, 2020.

- [12] A. E. Khateb, N. A. Rahim, J. Selvaraj, and B. W. Williams, "The effect of input current ripple on the photovoltaic panel efficiency," in *2013 IEEE Conference on Clean Energy and Technology (CEAT)*, pp. 478–481, 2013.

## Chapter 2

## Minimum Current-Ripple Point Tracking Control for Interleaved Dual Switched-Inductor DC-DC Converters

#### **Summary of the chapter**

In this chapter a research journal that presents a novel output current/ voltage control for interleaved DC-DC converters with dual switched input-inductors, i.e., interleaved input inductors controlled by independent switches is presented. The proposed approach is able to guarantee a minimum input-currentripple point tracking (MCRPT) despite of variations on the operating point. The controller encompasses three control stages: current stabilization, output-voltage regulation and minimum input-current-ripple control. In contrast with the two first loops, the latter is a novel stage introduced in this work to allow operation with minimum input-current-ripple in the whole operating region. That is, even though the converter has been designed for operation with minimum ripple in a given operating point, the scheme is able to dynamically deviate from this point to a new one where the ripple is minimized and the output voltage remains constant. The proposed scheme is experimentally validated using a laboratory prototype of a high-gain interleaved multilevel boost converter.

## Minimum Current Ripple Point Tracking Control for Interleaved Dual Switched-Inductor DC–DC Converters

Carlos A. Villarreal-Hernandez, Omar Fernando Ruiz-Martinez, Jonathan Carlos Mayo-Maldonado, Gerardo Escobar, Senior Member, IEEE, Jesus Elias Valdez-Resendiz, and Julio C. Rosas-Caro

Abstract—This article presents a novel output current/voltage control for interleaved dc-dc converters with dual switched input inductors, i.e., interleaved input inductors controlled by independent switches. The proposed approach is able to guarantee a minimum input current ripple point tracking despite of variations on the operating point. The controller encompasses three control stages: current stabilization, output-voltage regulation, and minimum input current ripple control. In contrast with the two first loops, the latter is a novel stage introduced in this article to allow operation with minimum input current ripple in the whole operating region. That is, even though the converter has been designed for operation with minimum ripple in a given operating point, the scheme is able to dynamically deviate from this point to a new one where the ripple is minimized and the output voltage remains constant. The proposed scheme is experimentally validated using a laboratory prototype of a high-gain interleaved multilevel boost converter.

Index Terms—Control, current ripple, interleaved dc-dc converters, modeling.

#### I. INTRODUCTION

RENEWABLE dc sources such as fuel cells, solar panels, etc., usually produce low and fluctuating output voltages, that are not suitable to directly feed grid-tied inverters. Consequently, dc—dc converters with high input-to-output voltage gain are required [1]–[3]. Among the desirable features of such converters, the use of moderate duty cycles to maintain high-efficiency is required, which is not possible to achieve with traditional converters. Another relevant issue in renewable

Manuscript received July 2, 2019; revised October 22, 2019; accepted November 28, 2019. Date of publication January 6, 2020; date of current version October 19, 2020. The authors would like to thank CONACyT and the Mexican Ministry of Energy (SENER) for their founding support under the project #266632, "Laboratorio Binacional para la Gestion Inteligente de la Sustentabilidad Energetica y la Formacion Tecnologica. (Corresponding author: Jonathan Carlos Mayo-Maldonado.)

- C. A. Villarreal-Hernandez, O. F. Ruiz-Martinez, J. C. Mayo-Maldonado, G. Escobar, and J. E. Valdez-Resendiz are with the School of Engineering and Sciences, Tecnologico de Monterrey, Monterrey 64849, Mexico (e-mail: carlosvillarreal920@gmail.com; omar\_ruiz@tec.mx; jcmayo@itesm.mx; gescobar@ieee.org; jesusvaldez@tec.mx).

- J. C. Rosas-Caro is with the Academia de Electrica, Electronica y Control, Universidad Panamericana, Zapopan 45010, Mexico (e-mail: crosas@up.edu.mx).

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TIE.2019.2962458

energy applications is the converter's input current ripple [4], which is an inherent component in boost converters playing a major role in efficiency and life-time of, e.g., photovoltaic (PV) panels and fuel cells (cf. [5], [6]).

It is precisely this issue that has motivated the flourishing of ripple-cancellation strategies where interleaved topologies (see e.g. [7]–[16]) are the most appealed solutions. However, it has been noticed that high input-to-output voltage gain solutions and input current ripple cancellation topologies are topics commonly studied separately (with a few existing plausible rounded approaches, e.g., [17]). In addition, a common shortcoming in interleaved converters is the restriction of having a fixed operating point at which the current-ripple is perfectly cancelled. This restriction implies that the duty cycle, and consequently the converter gain, cannot be freely selected, usually D=0.5. Hence, the current-ripple is reduced but not cancelled out outside a relatively small neighborhood of the zero current-ripple operating point. The following are examples of this restriction.

In [7]–[9], the authors propose controllers based on current-balancing and output voltage regulation with a restricted operating point. In [17], a linear controller for a double-dual boost converter is implemented, where duty cycles of the transistor stages are required to be equal. The work in [18] presents a linear controller that achieves perfect cancellation at a constrained operating point, with equal inductor currents. In [19], a linear closed-loop implementation that requires equal duty cycles is presented. In [20], a controller that involves proportional values duty cycles is presented. Needless to say, the closed-loop operation of the converters is crucial to deal with variations of, both input-voltage and load that are present in any realistic scenario (see e.g., [7], [18]–[21]).

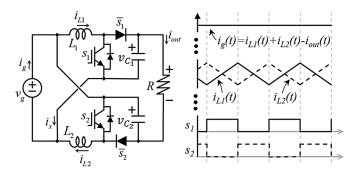

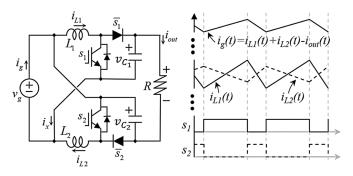

In some cases, the aforementioned constraint is enforced by interleaved topologies, where, although their input inductors are controlled by different switches, such switches cannot adopt arbitrary duty cycles. This is the case of, for example, the traditional two phase interleaved boost converter. However, there are other modern topologies that contain dual input inductors, where inductors are independently controlled, as in *double dual boost converters* (see [17], [22]). This is also the case in many other topologies, see e.g., the review of interleaved converters in [23]. Motivated by this issue, the pivotal argument in this article, is that there is no compelling reason to keep constraining

0278-0046 © 2019 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

the duty cycles in modern interleaved converters. Instead, this article proposes to exploit their emerging freedom coming from duality, to increase the current ripple cancellation capabilities of converters over a much wider operating region.

From the literature review, it has been observed that high input-to-output voltage gain converters, input current ripple mitigation and the appropriate control design are relevant topics for which there is still room for improvement. This article presents a complete solution for the above discussed issues, which comprises an interleaved topology of two multilevel dc–dc boost converters together with an appropriate controller overcoming disadvantages of some high input-to-output voltage gain topologies, and featuring input current ripple mitigation at any desirable operating region. It is shown that all these are achieved by the proper sizing of inductors and a suitable control law that minimizes the input current ripple in an *active* way.

In particular, a new control strategy is proposed, which is able to simultaneously regulate the output voltage and actively mitigate the input current ripple despite of variations in the operating point. Out of this, a new concept referred to as *minimum current ripple point tracking (MCRPT)* for interleaved converters is introduced. That is, the proposed control scheme steers duty cycles to a particular steady-state value, where the minimum possible input current ripple is guaranteed with respect to any operating point of a voltage-regulated converter. In order to do so, we provide the characterization of converter gains that ensure stability in terms of easy-to-construct LMIs, for which effective computational tools to find solutions can be used, such as the MATLAB toolbox Yalmip. The proposed scheme and the main theoretical achievements are validated via experimental results.

#### II. MAIN CONTRIBUTIONS

The contributions of the proposed MCRPT controller can be outlined as follows.

- Active minimization of the current ripple is achieved.

Which permits to operate the converter over a region instead of only an operating point, which is the traditional point of view in passive strategies.

- 2) The proposed control is dual. i.e., it permits to independently set up the controllers, which drops the restriction to use a single time constant. This permits a greater disturbance rejection capability since one controller is able to respond faster than the other, out of which the lagging effect of the dominant (slowest) time constant is bypassed.

- 3) Stability is rigorously guaranteed. This is supported via the above Lyapunov analysis and the fact that the proposed converter has only one equilibrium point (characterized by the gain equations), i.e., given a single equilibrium, local stability implies global stability.

- 4) There is room for accommodating further current/voltage regulation strategies. i.e., it is possible to replace current/voltage loops by other strategies or to select the gains in a different way. This can be done if additional objectives or optimization strategies are of special interest for a particular application.

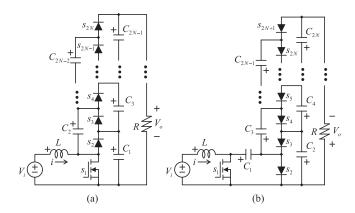

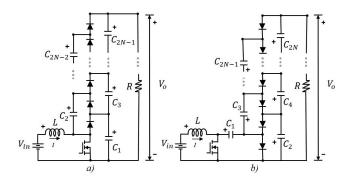

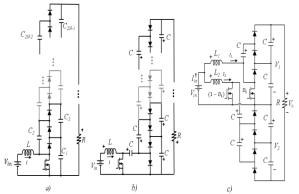

Fig. 1. (a) Multilevel boost converter. (b) Three-switch high voltage multilevel converter.

5) Further performance specifications can be easily accommodated. The proposed controller gain computation in terms of linear matrix inequalities (LMIs), permits to add further restrictions in the sense of optimal control. For instance, the LMI representation of functionals to enforce energy, time response, voltage/current variable relationships, and so forth.

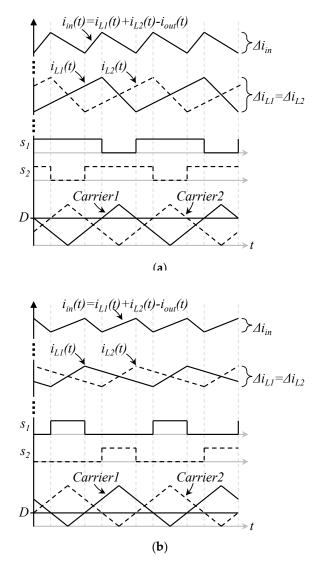

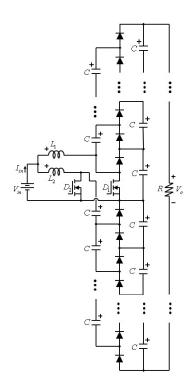

#### III. INTERLEAVED MULTILEVEL BOOST CONVERTER

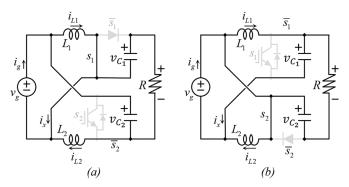

This section deals with the introduction and the modeling of a nonconventional *switched-capacitor* topology, where standard modeling techniques, such as averaging (in the sense of [24]), cannot be directly applied. This is a known shortcoming that is extensively discussed in [25]-[27]. To deal with this issue, we resort to a special nonstandard averaging technique based on a reduced-order modeling approach (see [27]–[29] with other plausible variations) that is instrumental for control purposes. The proposed interleaved topology is based on the combination of the multilevel boost converter proposed in [30] [see Fig. 1(a)] and a multilevel circuit derived from the Cuk converter proposed in [31] [see Fig. 1(b)]. These are hybrid topologies as they both comprise a step-up converter and multilevel stages based on switched capacitor multiplier cells. The resulting converters feature high gain, small size, high power density, and light weight due to the low voltage stress across (small size) components.

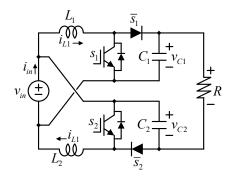

#### A. Interleaved Multilevel Boost Converter

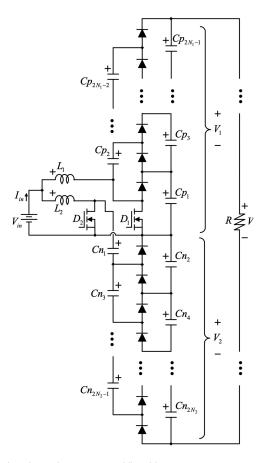

By interleaving the configurations in Fig. 1, the topology shown in Fig. 2 is obtained, which is referred to as the *interleaved multilevel boost converter* all along the article. The modeling of these type of topologies involves several challenges. First, an increased number of stages implying an increased number of equations; and second, a switched-capacitor dynamics, which cannot be modeled right away by *averaging* (cf. [32]), as explained in [25], [27] and [28].

For instance, according to [25], an average-loss approach can be alternatively used to model the converter in Fig. 1(a), where the equivalent *switch resistances* denoted by  $R_{\rm eq}$  are

Fig. 2. Interleaved  $N_1 + N_2$  multilevel boost converter.

explicitly used in the modeling process. By inspecting Fig. 1(a) the following set of equations are obtained as follows:

$$L\frac{d}{dt}i = V_{\text{in}} - (1-D)V_{C_1}$$

$$C_1\frac{d}{dt}V_{C_1} = (1-D)i - \frac{V_{C_1} - V_{C_2}}{R_{\text{eq}1}} - \frac{1}{R}\sum_{k=1}^{N}V_{C_{2k-1}}$$

$$C_2\frac{d}{dt}V_{C_2} = \frac{V_{C_1} - V_{C_2}}{R_{\text{eq}1}} - \frac{V_{C_2} - V_{C_3}}{R_{\text{eq}2}}$$

$$C_3\frac{d}{dt}V_{C_3} = \frac{V_{C_2} - V_{C_3}}{R_{\text{eq}2}} - \frac{V_{C_3} - V_{C_4}}{R_{\text{eq}3}} - \frac{1}{R}\sum_{k=1}^{N}V_{C_{2k-1}}$$

$$\vdots$$

$$C_{(2N-2)}\frac{d}{dt}V_{C_{2N-2}} = \frac{V_{2N-3} - V_{C_{2N-2}}}{R_{\text{eq}_{N-2}}} - \frac{V_{C_{2N-2}} - V_{C_{2N-1}}}{R_{\text{eq}_{N-1}}}$$

$$C_{(2N-1)}\frac{d}{dt}V_{C_{2N-1}} = \frac{V_{C_{2N-2}} - V_{C_{2N-1}}}{R_{\text{eq}N-1}} - \frac{1}{R}\sum_{k=1}^{N}V_{C_{2k-1}}. \quad (1)$$

where the parameter N denotes the number of multiplier levels, and  $R_{eq_i}$  represent equivalent resistances inducing (average) losses due to the energy transfer among capacitors (see [25], [26] for further details). To avoid the use of such an excessive number

of variables and equations, it is proposed to reduce the model order by assuming that every capacitance has the same value C, i.e.,  $C_i := C$ ,  $i \in \{1, 2, ...\}$ ; and that the (average) voltage across capacitors is always the same. This approximation is justified by the self-voltage-balancing property of the converter (see [27] for further details), i.e., it is assumed that

$$V_o = \sum_{k=1}^{N} V_{C_{2k-1}}; \ V_{C_1} \simeq V_{C_2} \simeq \dots \simeq V_{C_{2N-1}}.$$

(2)

As a result, the derivative of the voltage across the capacitors (that serve as energy transfer elements in Fig. 1, e.g.,  $C_2$  and  $C_{2N-2}$ ) is equal to zero, i.e., the voltage across such capacitors is practically constant, which is a common assumption whenever the switching frequency is sufficiently high (see, e.g., [27]). Then, by adding up the equations of the output capacitor voltages, the following reduced-order model is obtained as follows:

$$L\frac{d}{dt}i = V_{\rm in} - (1-D)V_{C_1}$$

$$\sum_{k=1}^{N} C\frac{d}{dt}V_{C_{2k-1}} = (1-D)i - \frac{1}{R}\sum_{k=1}^{N} V_{C_{2k-1}}.$$

(3)

By considering (2) and (3) can be expressed as follows:

$$L\frac{d}{dt}i = V_{\rm in} - \frac{(1-D)}{N}V_o$$

$$NC\frac{d}{dt}V_o = (1-D)i - N\frac{V_o}{R}.$$

(4)

Notice that this model is similar to that of a conventional boost converter, i.e., for N=1. Following the same considerations, a reduced-order model for the converter of Fig. 1(b) can be obtained. In fact, both models have identical structure. Consequently, an index term  $j \in \{1,2\}$  [j=1 for Fig. 1(a) and j=2 for Fig. 1(b)] is introduced to distinguish the effect of each model after the overall interleaved composed converter shown in Fig. 2. By adopting the notation of the general circuit in Fig. 2, then the overall model will remain for the rest of the article as follows:

$$L_j \frac{d}{dt} I_j = V_{in} - \left(\frac{1 - D_j}{N_j}\right) V_j , \quad j \in \{1, 2\}$$

$$N_j C \frac{d}{dt} V_j = (1 - D_j) I_j - N_j \left(\frac{V_o}{R}\right) \tag{5}$$

where  $I_{\text{in}} := I_1 + I_2$  represents the *total input current*, and  $V_o := V_1 + V_2$  represents the total output voltage.

It can be easily verified that the total steady-state gain of the converter is given by

$$G := \frac{N_1}{1 - D_1} + \frac{N_2}{1 - D_2} \ . \tag{6}$$

#### B. Sizing of the Inductors

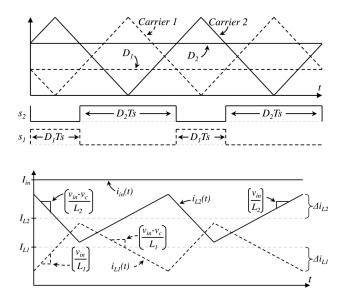

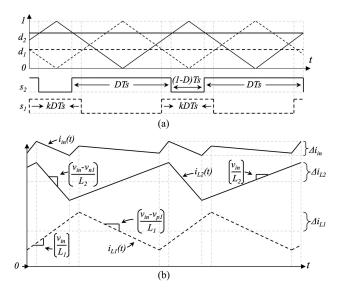

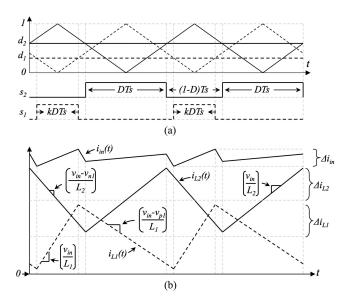

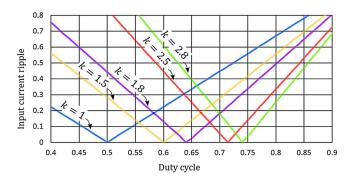

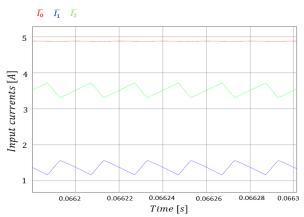

One of the main interests while implementing interleaved converters is the mitigation of the input current ripple denoted by  $\Delta I_{\rm in}$ . This is usually achieved by a convenient switching coordination between the involved converters. For instance, a perfect ripple cancellation is achieved when using complementary duty cycles and complementary switching signals as those

Fig. 3. Operating condition for total ripple cancellation.

Fig. 4. PWM signals with overlapped switching functions.

shown in Fig. 3. In what follows, it is shown how this can be achieved for any desirable operating point provided an adequate inductors size specification.

The pulsewidth modulation (PWM) signals of the converters are generated by two triangular carriers, each of them associated with different duty cycles, see Fig. 3. The phase among triangular carriers as well as among firing signals is  $180^{\circ}$  degrees. In an ideal case, for a certain duty cycle, the input current ripple can be completely suppressed, this is shown in Fig. 3, in which  $D_1 = (1 - D_2)$  and vice-versa.

In some cases, either the switching functions can be overlapped at certain values of duty cycles, or the value of duty cycle can produce dead times. The current waveforms corresponding to the former and the latter cases are illustrated in Figs. 4 and 5.

Consider the interleaved converter shown in Fig. 2. If the PWM carriers maintain a 180° phase shift with respect to

Fig. 5. PWM signals when switching functions are separated by a dead time.

each other, then the total current ripple can be computed as  $\Delta I_{\rm in} = \Delta I_1 - \Delta I_2$ , i.e.,

$$\Delta I_{\rm in} = \frac{V_{\rm in} D_1}{2f_s L_1} - \frac{V_{\rm in} D_2}{2f_s L_2} \ . \tag{7}$$

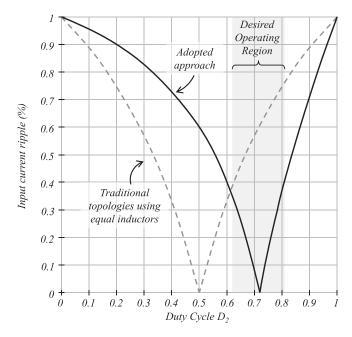

From (7), it can be noticed that in order to obtain  $\Delta I_{\rm in}=0$  (perfect ripple cancellation), it is required either to constrain the values of duty cycles  $D_1$  and  $D_2$ , which consequently will limit the gain of the converter (as usually done in traditional interleaved converters), or to design inductors  $L_1$  and  $L_2$  satisfying the following relation:

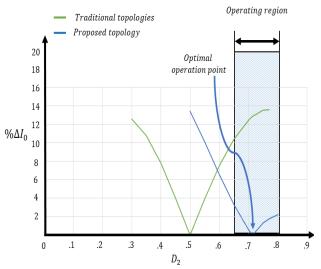

$$L_2 = L_1 \left(\frac{D_2}{D_1}\right) . (8)$$

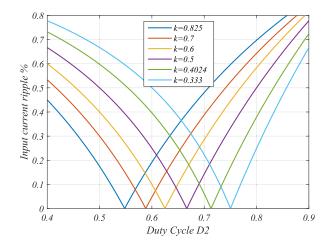

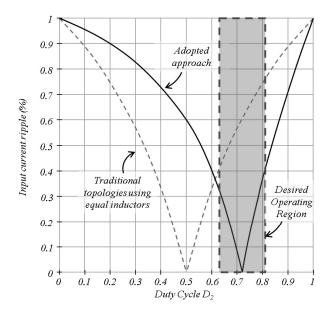

This allows to select any pair of arbitrary duty cycles and to compute the corresponding value of  $L_i$ ,  $i \in \{1,2\}$ . The latter yields a design approach that, first, does not restrict the gain of the converter and, second, allows a free selection of the operating point with  $\Delta I_{\rm in}=0$ . This idea has been exploited in [33] for an open-loop operation, and its advantage against traditional approaches is illustrated in Fig. 6. For example, there is not any restriction to select and deal with a gain induced by  $D_2=0.713$ , which may come out of a given specification. In general, there is a significant improvement in ripple cancellation around a selected operating region with different inductors, as compared to the current ripple obtained by traditional approaches.

In this article, this current ripple cancellation approach associated with the design of converters is the pivotal figure of the proposed MCRPT control technique. The following section provides the details of the closed-loop analysis.

#### IV. CURRENT AND VOLTAGE CONTROL DESIGN

This section studies the dynamics of the converter for the design of stabilizing controllers.

Fig. 6. Ripple level comparison under different design conditions.

#### A. Modeling Specification

As discussed in the previous section, the proposed converter is designed to operate under a fixed (but otherwise arbitrary) operating region, for which the input current ripple is minimized. Hence, we use the linear version of the model in (5) in order to design controllers able to guarantee stability and performance over such desired region. The model is now formulated in terms of incremental variables in state-space form, which yields

$$\frac{d}{dt} \begin{bmatrix} \Delta I_j \\ \Delta V_j \end{bmatrix} = \underbrace{\begin{bmatrix} 0 & \frac{(1 - \overline{D}_j)}{N_j L_j} \\ \frac{(1 - \overline{D}_j)}{N_j C} & \frac{N_j}{RC_j} \end{bmatrix}}_{=:A_j} \begin{bmatrix} \Delta I_j \\ \Delta V_j \end{bmatrix} + \underbrace{\begin{bmatrix} \overline{V}_j \\ \overline{N_j L_j} \\ -\overline{i}_j \\ \overline{C} \end{bmatrix}}_{=:B_j} \Delta D_j$$

where  $\Delta I_j := I_j - \bar{i}_j$  is the incremental value of the variable  $I_j$ , with respect to its desired value  $\bar{i}_j$  at steady state, with j=1,2. The rest of the variables are thus defined analogously.

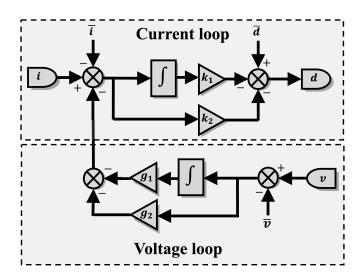

#### B. Input Current and Output Voltage Control

The controller must guarantee regulation of the output voltage toward a constant or variant reference. However, it is well-known that boost converters have a *nonminimum phase characteristic* with respect to the output voltage, i.e., the corresponding duty cycle-to-voltage transfer function has a zero in the right half plane. This situation implies a reduction on the controller bandwidth, which limits the parametric selection of closed-loop gains (see [34, Sec. 5.6]) and acts as a potential instability mechanism (see [32], [35]). An alternative, which is usual in practice, consists in indirectly regulate the output voltage by directly regulating the inductor current which is of minimum phase.

The input current control loop is implemented by the following *PI controllers* for both converters:

$$\Delta D_j := -k_{j,1} x_j - k_{j,2} \Delta I_j; \quad j = 1, 2 \tag{10}$$

where  $k_{j,1}$ ,  $k_{j,2}$  are the controller gains;  $x_j$ , is the integral of the error of the variable  $\Delta I_j$  with respect to a reference  $i_{\text{ref},j}$ , j = 1, 2; and whose state-space equation is given by

$$\frac{d}{dt}x_j = \Delta I_j - i_{\text{ref},j}; \quad j = 1, 2.$$

(11)

The output-voltage loop is analogously defined in a nested form in order to ensure voltage stabilization at the desired operating point, i.e.,

$$i_{\text{ref},j} := -g_{j,1}z_j - z_{j,2}\Delta V_j; \quad j = 1,2$$

(12)

where  $g_{j,1}$  and  $g_{j,2}$  are the controller gains, and  $z_j$ , j=1,2, is the integral of the error variable  $\Delta V_j = V_j - \overline{V}_j$  with respect to zero; or equivalently the integral of the error between the voltage  $V_j$  and its desired reference  $\overline{V}_j$ , j=1,2; and whose state-space equation is given by

$$\frac{d}{dt}z_j = \Delta V_j = V_j - \overline{V}_j; \quad j = 1, 2.$$

(13)

#### C. Controller Gain Tuning to Ensure Stability

Once the controller scheme has been proposed, the controller gains are tune to guarantee stability in terms of a set of LMIs derived from the *Lyapunov stability theorem* (see [36], Section 7.4).

Using (9) and the controller (10), (11) and (12), (13), the model can be reformulated with an extended state space as follows:

$$\frac{d}{dt} \begin{bmatrix} \Delta I_j \\ \Delta V_j \\ x_j \\ z_j \end{bmatrix} = \underbrace{\begin{bmatrix} A_j - k_{j,2} B_j [1 \ 0] & -k_{j,1} B_j & 0_{2 \times 1} \\ [1 \ g_{j,2}] & 0 & g_{j,1} \\ [0 \ 1] & 0 & 0 \end{bmatrix}}_{=:\widetilde{A}_j} \begin{bmatrix} \Delta I_j \\ \Delta V_j \\ x_j \\ z_j \end{bmatrix}$$

with j=1,2; hence the closed-loop system can be represented by the matrix  $\widetilde{A}_j$ . As stated in [36, Theorem 7.4.4, pp. 263–264] this closed-loop system is asymptotically stable if there exists a matrix  $P_j > 0$ , j=1,2, of suitable size such that

$$Q_j := \widetilde{A}_j^{\top} P_j + P_j \widetilde{A}_j < 0; \quad j = 1, 2.$$

(15)

Since the parameters of both  $P_j$  and  $\widetilde{A}_j$  (the controller gains) are unknown, condition (15) is a bilinear matrix inequality, for which iterative algorithms can be employed to find suboptimal solutions (see [37]). This is actually a straightforward matter for solvers such as Yalmip.

Since the inequality (15) provides a family of solutions corresponding to different left-half plane eigenvalues and consequently different time constants; we now provide a way to characterize all solutions. This is possible since according to [38, Theorem 3.3], there exists a positive constant  $\epsilon_i$  such that

$$Q_i - 2\epsilon_i P_i < 0; \quad j = 1, 2.$$

(16)

Since  $P_j > 0$ , then it can be factorized as  $P_j := N_j^{\top} N_j$ , where  $N_j$  is square and nonsingular. Consequently, inequality (16) can be written as

$$N_j^{-T}Q_jN_j - 2\epsilon_j I < 0; \quad j = 1, 2$$

(17)

Hence,  $\epsilon_j < -\frac{1}{2}\lambda_{\max}$ , where  $-\lambda_{\max}$  is the largest eigenvalue of  $N_j^{-T}Q_jN_j$ , j=1,2 in (17). Consequently,  $\epsilon_j$  must necessarily belong to an interval  $[0,-\frac{1}{2}\lambda_{\max}]$ . In short, by modifying the value of  $\epsilon$ , we obtain different solutions of (15) from which we can chose the most suitable time constant for  $A_j$ , j=1,2, according to our desired dynamic response.

#### V. MINIMUM CURRENT RIPPLE POINT TRACKING

The control set-up, introduced in the previous section, can be used to implement any technique currently available in the literature for interleaved converters, e.g., current balancing, equal, or complementary duty cycles, etc. We now introduce an additional control law that is able to guarantee input current minimization. This is in sharp contrast with the rest of the schemes whose operating point cannot be freely chosen and whose controller does not minimize the current ripple when the converters deviate from such point.

This strategy is called *MCRPT* technique. Based on the findings presented in Section III-B, it is proposed an implementation that adds additional constraints to the controllers introduced in Section IV, i.e., to achieve input current stabilization and output-voltage control, while featuring the least possible percentage of input current ripple at any operating point.

This technique can be applied to any interleaved topology with dual input switched inductors, i.e., converters with the following.

- 1) Two input inductors controlled by different switches.

- 2) Switches are able to adopt different duty cycles.

This is the case of plenty of emerging topologies (see, e.g., the case of double dual boost converters [17], [22] and the compendium of topologies included as a review in [23].

Based on this premises, we consider an interleaved converter whose inductances have a relationship given in (8), and whose PWM carriers are in counter phase. This yields the following relationship:

$$k := \frac{L_1}{L_2} = \frac{D_1}{D_2}. (18)$$

The concept of MCRPT follows from (18), which establishes the following duty cycle relationship:

$$D_1 = kD_2. (19)$$

Fig. 7 depicts curves that show the zero ripple points in terms of the design parameter k, and how the ripple level increases when the operating point moves away. Notice that the small amount of ripple on the input current is an advantage that follows the design of the converter according to a preselected minimum ripple point, while the condition (19) can be satisfied via an active MCRPT technique that "chases" the curve.

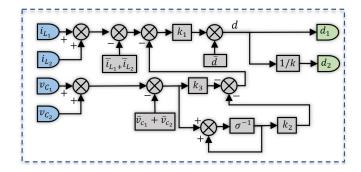

For the MCRPT application, an additional controller is considered to link both multilevel converter controllers to guarantee output voltage regulation, plus an additional condition

Fig. 7. MCRPT curves according to inductors relationship, i.e., curves of input ripple as a function of the duty cycle for different values of k.

satisfying (19). To implement the MCRPT scheme (the third stage), the following control law is introduced:

$$\frac{d}{dt}w = D_1 - kD_2 \tag{20}$$

where w is a variable that implements the, so called, MCRPT. The following additional term is introduced to the output-voltage loops as follows:

$$i_{\text{ref}_1} = -g_{1_1}V_1 - g_{2_1}z_1 + g_3w$$

$$i_{\text{ref}_2} = -g_{1_2}V_2 - g_{2_2}z_2 - g_3w.$$

(21)

Notice that, based on (21), the currents set-points are function of both the output voltages and w. The MCRPT law steers the duty cycles to a point that satisfies condition (19).

The rationale behind the proposition of (20) is the accomplishment of condition (19), which is possible in steady state [(20) becomes (19)] as long as the gain  $g_3$  is suitably selected in such a way that the whole closed-loop system is asymptotically stable. In order to guarantee such stable operation, we can simply further extend the models (22) by including (20), which yields

$$\frac{d}{dt} \begin{bmatrix} \Delta I_1 \\ \Delta V_1 \\ x_1 \\ z_1 \\ \Delta I_2 \\ \Delta V_2 \\ x_2 \\ z_2 \\ w \end{bmatrix} = \underbrace{\begin{bmatrix} \widetilde{A}_1 & 0_{4 \times 4} & \begin{bmatrix} 0 \\ -g_3 \\ 0_{2 \times 1} \end{bmatrix} \begin{bmatrix} \Delta I_1 \\ \Delta V_2 \\ x_1 \\ z_2 \\ \Delta I_1 \\ \Delta V_2 \\ \Delta I_1 \\ \Delta V_2 \\ x_1 \\ \Delta V_2 \\ x_1 \\ z_2 \end{bmatrix}}_{=:\widetilde{A}} (22)$$

where

$$\widetilde{D}_1 := [-k_{1,2} \ 0 \ -k_{1,1} \ 0]$$

$\widetilde{D}_2 := [-k_{2,2} \ 0 \ -k_{2,1} \ 0].$

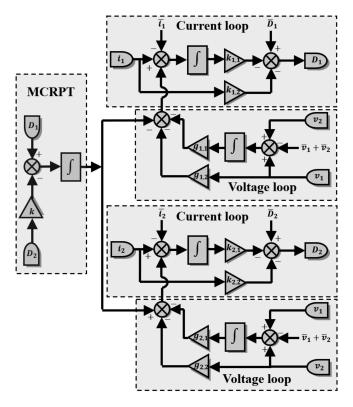

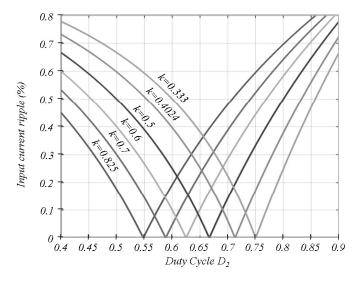

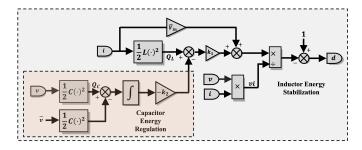

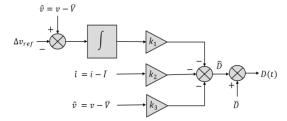

Fig. 8. Proposed control strategy encompassing current/voltage loops and MCRPT.

Note that an important implication of (22) is that the resulting full closed-loop system (including the MCRPT loop) is *autonomous*. This means that the future of the system is completely determined by its past, i.e., the system is *causal* (see [36, Sec. 3.2]). Consequently, although the duty cycles are involved in the computation of the control law, its implementation can be carried out as in any other traditional closed-loop controller, where current initial conditions are used to compute future input values.

Finally, the full set of gains can be computed in an analogous way as in Section IV, i.e., by finding a matrix P>0 of suitable size, such that

$$Q := \widetilde{A}^{\top} P + P \widetilde{A} < 0. \tag{23}$$

which can be easily done by using Yalmip. Finally, we illustrate the full schematic of the controller in Fig. 8.

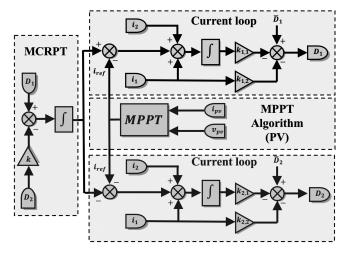

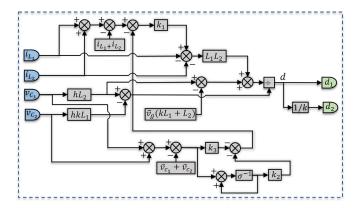

#### A. Other Configurations: Current Control and MPPT

In some cases, we might be interested in the combination of the MCRPT technique with a MPPT algorithm, as in the case of photovoltaic systems. In this case, any MPPT can be used. The diagram in Fig. 8 is simplified to adopt a current control mode. The current control is thus driven by the selected MPPT technique while maintaining the same rationale of gain computation. The resulting configuration is illustrated in Fig. 9.

Note that both *voltage regulation* (see Fig. 8) and *MPPT* (see Fig. 9) act upon a current controller, as well as the proposed

Fig. 9. Proposed MCRPT control strategy simultaneously operating with any suitable maximum power point tracking (MPPT) technique for a photovoltaic system with current  $i_{\rm pv}$  and voltage  $v_{\rm pv}$ .

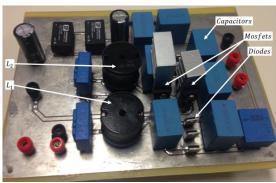

TABLE I

PARAMETERS OF THE EXPERIMENTAL SETUP

| Parameter                           | Value           |

|-------------------------------------|-----------------|

| $L_1$                               | $237~\mu H$     |

| $L_2$                               | 90 μΗ           |

| C                                   | $10~\mu F$      |

| Mosfets                             | IRFP250         |

| Diodes                              | BYW29E-400      |

| Resistance                          | 500 Ω           |

| $N_1,N_2$                           | 2               |

| PWM frequency                       | 50kHz           |

| ADC sampling                        | 200kHz          |

| Integration step                    | $5\mu s$        |

| $V_{in}$                            | 24 V            |

| $V_{out}$                           | 192 V           |

| $k = L_1/L_2$                       | 2.633           |

| $\overline{D}_1$ , $\overline{D}_2$ | 0.627,0.238     |

| $\overline{V}_1$ , $\overline{V}_2$ | 128.97V, 63.02V |

| $\overline{I}_1$ , $\overline{I}_2$ | 2.06A, 1A       |

|                                     |                 |

MCRPT control. Consequently, it is possible to interchange objectives that define a current reference without conflict.

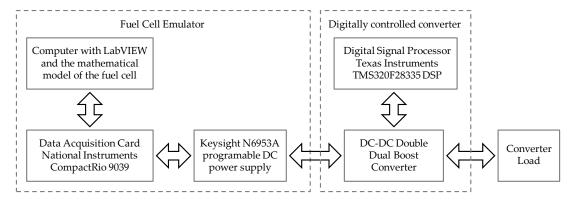

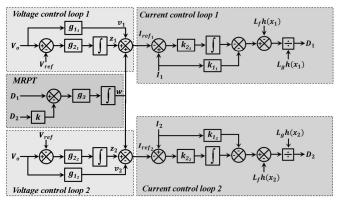

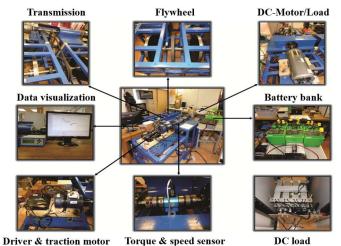

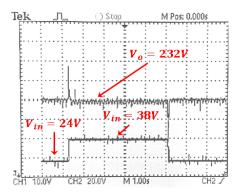

#### VI. EXPERIMENTAL SETUP AND VALIDATION

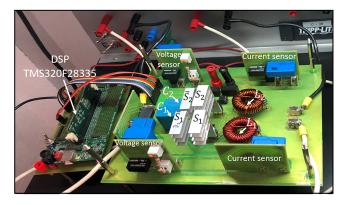

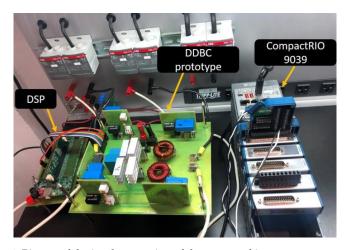

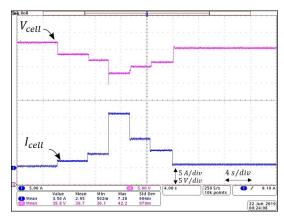

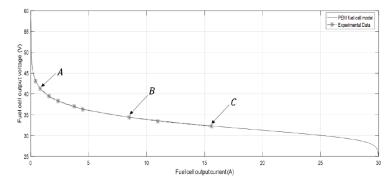

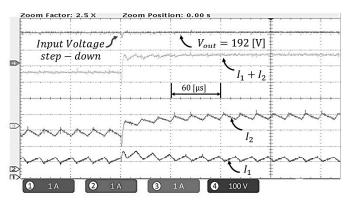

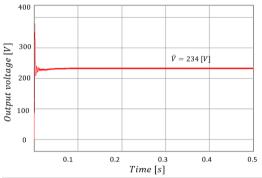

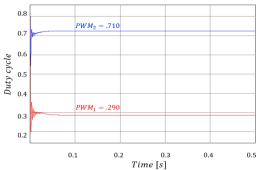

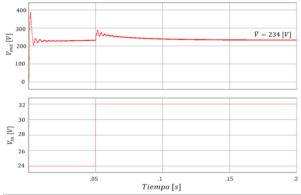

The proposed controller was validated using an experimental prototype of a four-level version of the converter in Fig. 2, i.e.,  $N_1=2$  and  $N_2=2$ . It comprises an electronic load at the output and a digital signal processor TI TMS320F28335 as the control platform. The parameters of the converter as well as other useful information about the implementation are shown in Table I.

In order to avoid compromising the stability properties and the performance of the controller that were achieved in the theoretical analysis, it must be guaranteed that the *Nyquist*

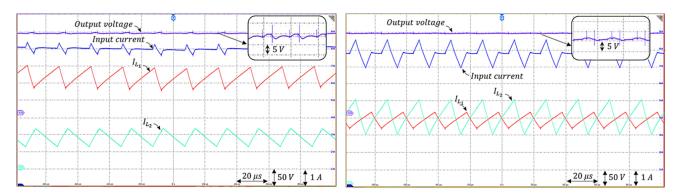

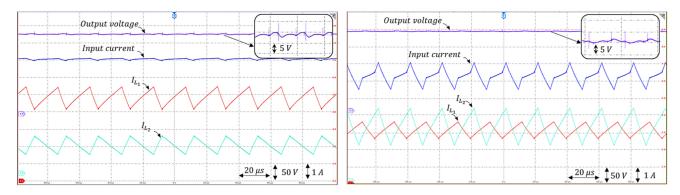

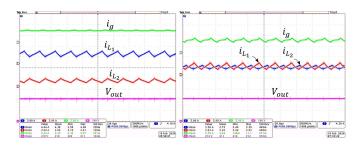

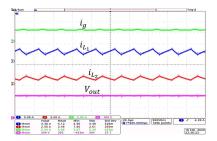

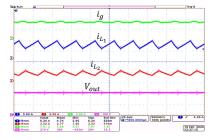

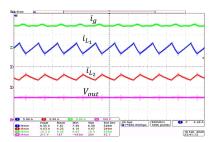

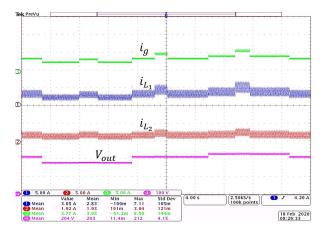

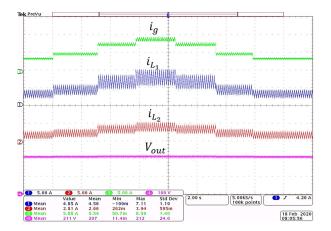

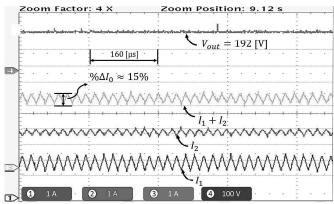

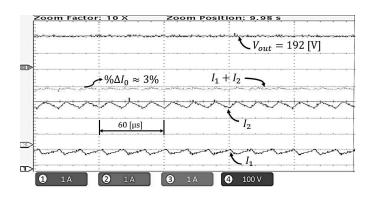

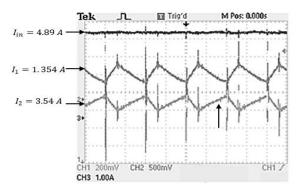

Fig. 10. Experimental results at  $V_{\rm in}=20\,{\rm V}$  of input current ripple cancellation using the proposed MCRPT (left) and without it, by applying traditional current balancing (right).

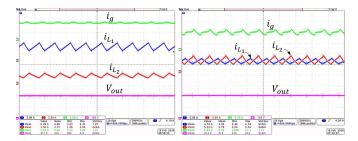

Fig. 11. Experimental results at  $V_{\rm in}=$  24 V of input current ripple cancellation using the proposed MCRPT (left) and without it, by applying traditional current balancing (right).

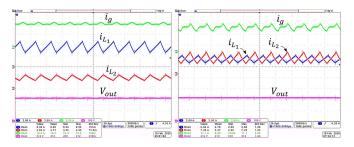

Fig. 12. Experimental results at  $V_{\rm in}=30\,{\rm V}$  of input current ripple cancellation using the proposed MCRPT (left) and without it, by applying traditional current balancing (right).

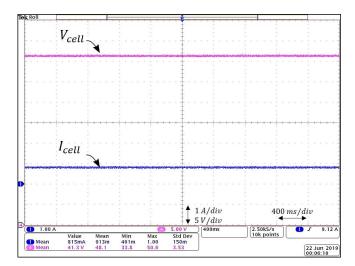

frequency criterion is satisfied, namely, that the continuous-time signals are sampled at a frequency that is at least twice the value of the switching frequency (see [39, Sec. 2.2]). In this case, the digital signal processor set-up permits a sample frequency equal to 100 kHz, i.e., twice the switching frequency. The controller gains were obtained by solving the inequality (23) using Yalmip. The controller gains used in this work are:  $k_{1,1} = 0.198$ ,  $k_{1,2} = 0.112$ ,  $g_{1,1} = 18$ ,  $g_{1,2} = 18.8$ ,  $k_{2,1} = 0.038$ ,  $k_{2,2} = 0.012$ ,  $g_{2,1} = 3.5$ ,  $g_{2,2} = 6.3$ , and  $g_3 = 1100$ .

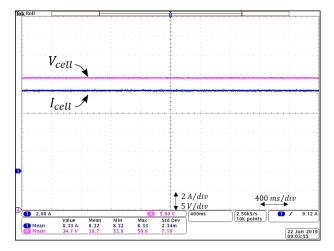

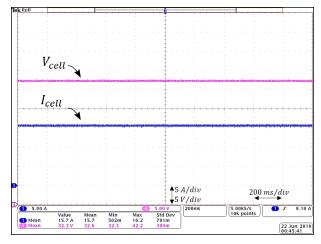

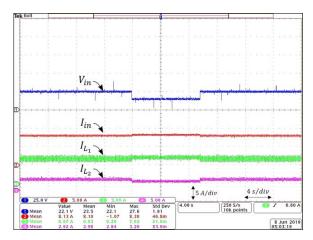

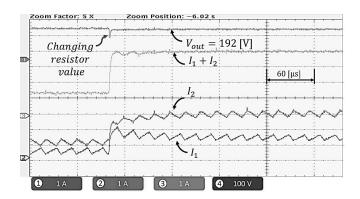

As previously stated, the main advantage of the presented controller is its ability to reach an operating point such that the minimum ripple condition is guaranteed, while preserving voltage regulation. For validation purposes, a controller featuring the traditional approach, namely, current balancing (cf., [7]–[9]) is implemented and compared with the propose MCRPT controller using the same converter. To corroborate that the proposed MCRPT control strategy always achieves minimum ripples, the topology is operated under variations of the input voltage: 20 V, 24 V, 30 V, which involves a significant change in the input current due to the high voltage gain of the converter. The results are shown in Figs. 10–12. The experimental results also contain the output voltage ripple to corroborate that it is

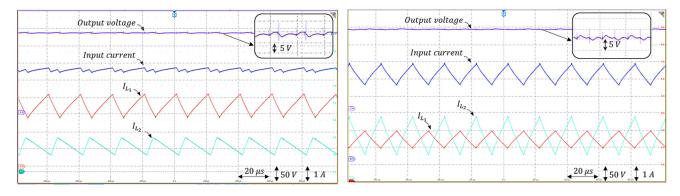

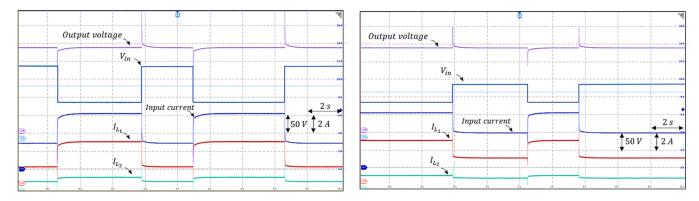

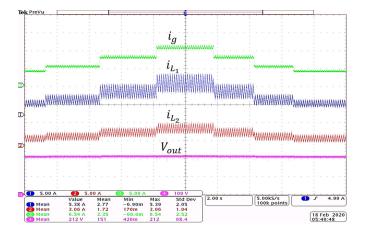

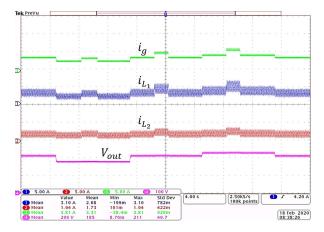

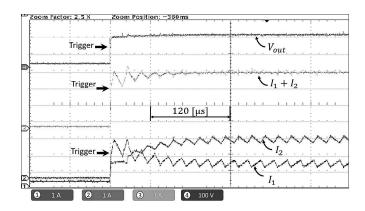

Fig. 13. Dynamical response of the MCRPT under abrupt variations on the input voltage: 20–40 V and vice versa (left) and 30–40 V and vice versa (right).

Fig. 14. Dynamical response of the MCRPT under abrupt variations on the output load from 45 to 100% and vice versa.

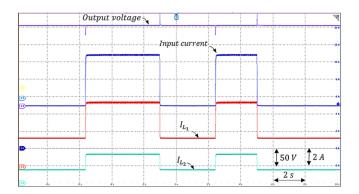

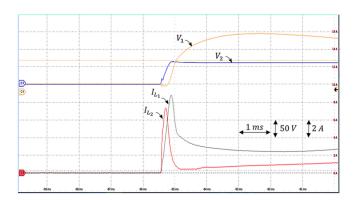

Fig. 15. Dynamic response from zero initial conditions.

not affected by the current ripple cancellation technique. Notice that although both controllers achieve the same output voltage 200 V, only the MCRPT is able to minimize the current ripple by searching for the minimum ripple condition  $D_1=kD_2$ , despite of input voltage changes.

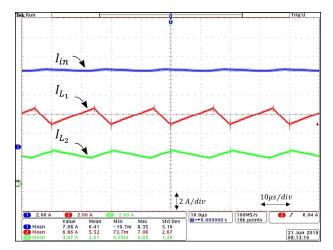

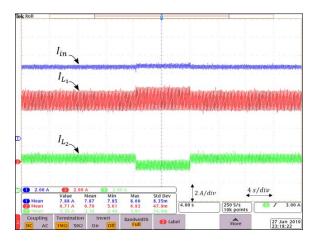

In Fig. 13, we show the full dynamics of the converter to validate its robustness of the output voltage regulation against continuous variations in the input voltage between 20 V– and 40 V and 20 V– and 30 V. Moreover, the robustness of the MCRPT algorithm to search the optimal current ripple cancellation condition. Notice that the steady-state traces (zooming in)

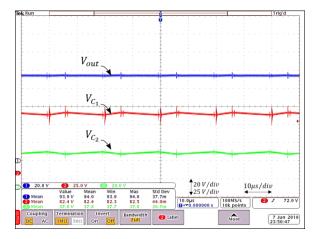

correspond to the results previously shown in of the steady-state experiments previously shown in Figs. 10–12. Finally, Fig. 14 depicts experimental results show that the dynamical response of the converter with respect to abrupt load changes. We start with a nominal value  $R=400~\Omega$  and then we change repeatedly to  $180~\Omega$  and  $400\Omega$ , which corresponds to variations of 45 to 100% of nominal load and vice versa.

In order to show the dynamic performance of the converter, we present the initial transient from zero initial conditions with an output voltage set point equal to 200 V and an input voltage equal to 24 V, see Fig. 15.

#### VII. CONCLUSION

In this article, a MCRPT control scheme was proposed. Such control law contains a correction term that gradually deviates the operating point of duty cycles toward a point where minimum input current ripple can be achieved. That is, a new approach was adopted to guarantee current ripple cancellation for which duty cycles were not constrained as in the strategies currently available in the literature. We showed that the active minimum input current ripple point tracking implementation permits a minimum current-ripple despite of a variable operating point. Experimental results showed that the proposed scheme was able to simultaneously achieve input current stabilization, output voltage regulation and input current ripple minimization despite of disturbances such as input voltage and load changes.

#### **REFERENCES**

- [1] M. Lakshmi and S. Hemamalini, "Nonisolated high gain DC–DC converter for DC microgrids," *IEEE Trans. Ind. Electron.*, vol. 65, no. 2, pp. 1205–1212, Feb. 2018.

- [2] R. H. Ashique and Z. Salam, "A high-gain, high-efficiency non-isolated bidirectional DC-DC converter with sustained ZVS operation," *IEEE Trans. Ind. Electron.*, vol. 65, no. 10, pp. 7829–7840, Oct. 2018.

- [3] M. R. Banaei and S. G. Sani, "Analysis and implementation of a new sepic-based single-switch buck-boost DC-DC converter with continuous input current," *IEEE Trans. Power Electron.*, vol. 33, no. 12, pp. 10 317–10 325, Dec. 2018.

- [4] V. A. K. Prabhala, P. Fajri, V. S. P. Gouribhatla, B. P. Baddipadiga, and M. Ferdowsi, "A DC–DC converter with high voltage gain and two input boost stages," *IEEE Trans. Power Electron.*, vol. 31, no. 6, pp. 4206–4215, Jun. 2016.

- [5] A. E. Khateb, N. A. Rahim, J. Selvaraj, and B. W. Williams, "The effect of input current ripple on the photovoltaic panel efficiency," in *Proc. IEEE Conf. Clean Energy Technol.*, Nov. 2013, pp. 478–481.

- [6] S. K. Mazumder, R. K. Burra, and K. Acharya, "A ripple-mitigating and energy-efficient fuel cell power-conditioning system," *IEEE Trans. Power Electron.*, vol. 22, no. 4, pp. 1437–1452, Jul. 2007.

- [7] H. Chen, C. Lu, and U. S. Rout, "Decoupled master-slave current balancing control for three-phase interleaved boost converters," *IEEE Trans. Power Electron.*, vol. 33, no. 5, pp. 3683–3687, May 2018.

- [8] M. H. Mahmud, Y. Zhao, and Y. Zhang, "A sliding mode duty-ratio control with current balancing algorithm for interleaved buck converters," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, Mar. 2018, pp. 2281–2287.

- [9] H. Chen, C. Lu, and L. Huang, "Decoupled current-balancing control with single-sensor sampling-current strategy for two-phase interleaved boosttype converters," *IEEE Trans. Ind. Electron.*, vol. 63, no. 3, pp. 1507–1518, Mar. 2016.

- [10] M. Amiri and H. Farzanehfard, "A high-efficiency interleaved ultra-high step-down DC–DC converter with very low output current ripple," *IEEE Trans. Ind. Electron.*, vol. 66, no. 7, pp. 5177–5185, Jul. 2019.

- [11] B. Akhlaghi, N. Molavi, M. Fekri, and H. Farzanehfard, "High step-up interleaved ZVT converter with low voltage stress and automatic current sharing," *IEEE Trans. Ind. Electron.*, vol. 65, no. 1, pp. 291–299, Jan. 2018.

- [12] M. Amiri, H. Farzanehfard, and E. Adib, "A nonisolated ultrahigh step down dc-dc converter with low voltage stress," *IEEE Trans. Ind. Electron.*, vol. 65, no. 2, pp. 1273–1280, Feb. 2018.

- [13] J. Roy, Y. Xia, and R. Ayyanar, "High step-up transformerless inverter for AC module applications with active power decoupling," *IEEE Trans. Ind. Electron.*, vol. 66, no. 5, pp. 3891–3901, May 2019.

- [14] M. C. Mira, Z. Zhang, A. Knott, and M. A. E. Andersen, "Analysis, design, modeling, and control of an interleaved-boost full-bridge three-port converter for hybrid renewable energy systems," *IEEE Trans. Power Electron.*, vol. 32, no. 2, pp. 1138–1155, Feb. 2017.

- [15] Y. Huang, S. Tan, and S. Y. Hui, "Multiphase-interleaved high step-up DC/DC resonant converter for wide load range," *IEEE Trans. Power Electron.*, vol. 34, no. 8, pp. 7703–7718, Aug. 2019.

- [16] Y. Zhang, Y. Gao, J. Li, and M. Sumner, "Interleaved switched-capacitor bidirectional dc-dc converter with wide voltage-gain range for energy storage systems," *IEEE Trans. Power Electron.*, vol. 33, no. 5, pp. 3852– 3869, May 2018.

- [17] F. S. Garcia, J. A. Pomilio, and G. Spiazzi, "Modeling and control design of the interleaved double dual boost converter," *IEEE Trans. Ind. Electron.*, vol. 60, no. 8, pp. 3283–3290, Aug. 2013.

- [18] Y. Huangfu, S. Zhuo, F. Chen, S. Pang, D. Zhao, and F. Gao, "Robust voltage control of floating interleaved boost converter for fuel cell systems," *IEEE Trans. Industry Appl.*, vol. 54, no. 1, pp. 665–674, Jan. 2018.

- [19] P. Antoszczuk, R. G. Retegui, M. Funes, and D. Carrica, "Optimized implementation of a current control algorithm for multiphase interleaved power converters," *IEEE Trans. Ind. Informat.*, vol. 10, no. 4, pp. 2224–2232, Nov. 2014

- [20] C. A. Villarreal-Hernandez, J. C. Mayo-Maldonado, J. E. Valdez-Resendiz, and J.C. Rosas-Caro, "Modeling and control of an interleaved dc-dc multilevel boost converter," in *Proc. IEEE 18th Workshop Control Model. Power Electron.*, Jul. 2017, pp. 1–6.

- [21] N. Genc and I. Iskender, "DSP-based current sharing of average current controlled two-cell interleaved boost power factor correction converter," *IET Power Electron.*, vol. 4, no. 9, pp. 1015–1022, Nov. 2011.

- [22] D. B. Viet, Y. Lembeye, J. P. Ferrieux, J. Barbaroux, and Y. Avenas, "New high power-high ratio non isolated dc-dc boost converter for fuel cell applications," in *Proc. 37th IEEE Power Electron. Specialists Conf.*, Jun. 2006, pp. 1–7.

- [23] J. Chen, C. Wang, J. Li, C. Jiang, and C. Duan, "An input-parallel-output-series multilevel boost converter with a uniform voltage-balance control strategy," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 7, no. 4, pp. 2147–2157, Dec. 2019.

- [24] R. W. Erickson and D. Maksimovic, Fundamentals of Power Electronics. Berlin, Germany: Springer, 2007.

- [25] S. Ben-Yaakov, "On the influence of switch resistances on switched-capacitor converter losses," *IEEE Trans. Ind. Electron.*, vol. 59, no. 1, pp. 638–640, Jan. 2012.

- [26] M. Evzelman and S. Ben-Yaakov, "Average-current-based conduction losses model of switched capacitor converters," *IEEE Trans. Power Electron.*, vol. 28, no. 7, pp. 3341–3352, Jul. 2013.

- [27] J. C. Mayo-Maldonado, J. C. Rosas-Caro, and P. Rapisarda, "Modeling approaches for DC–DC converters with switched capacitors," *IEEE Trans. Ind. Electron.*, vol. 62, no. 2, pp. 953–959, Feb. 2015.

- [28] F. H. Dupont, C. Rech, R. Gules, and J. R. Pinheiro, "Reduced-order model and control approach for the boost converter with a voltage multiplier cell," *IEEE Trans. Power Electron.*, vol. 28, no. 7, pp. 3395–3404, Jul. 2013.

- [29] M. Das and V. Agarwal, "Generalized small signal modeling of coupled-inductor-based high-gain high-efficiency DC-DC converters," *IEEE Trans. Industry Appl.*, vol. 53, no. 3, pp. 2257–2270, May 2017.

- [30] J. C. Rosas-Caro, J. M. Ramirez, F. Z. Peng, and A. Valderrabano, "A DC–DC multilevel boost converter," *IET Power Electron.*, vol. 3, no. 1, pp. 129–137, 2010.

- [31] D. Zhou, A. Pietkiewicz, and S. Cuk, "A three-switch high-voltage converter," *IEEE Trans. Power Electron.*, vol. 14, no. 1, pp. 177–183, Jan. 1999.

- [32] H. Sira-Ramírez and R. Silva-Ortigoza, *Control Design Techniques in Power Electronics Devices*. Berlin, Germany: Springer, 2006.

- [33] J. C. Rosas-Caro, F. Mancilla-David, J. C. Mayo-Maldonado, J. M. Gonzalez-Lopez, H. L. Torres-Espinosa, and J. E. Valdez-Resendiz, "A transformer-less high-gain boost converter with input current ripple cancelation at a selectable duty cycle," *IEEE Trans. Ind. Electron.*, vol. 60, no. 10, pp. 4492–4499, Oct. 2013.

- [34] S. Skogestad and I. Postlethwaite, *Multivariable Feedback Control: Analysis and Design*, vol. 2. New York, NY, USA: Wiley, 2007.

- [35] J. C. Mayo-Maldonado, R. Salas-Cabrera, J. C. Rosas-Caro, J. D. Leon-Morales, and E. N. Salas-Cabrera, "Modelling and control of a dc-dc multilevel boost converter," *IET Power Electron.*, vol. 4, no. 6, pp. 693–700, Jul. 2011.

- [36] J. Polderman and J. Willems, Introduction to Mathematical System Theory: A Behavioral Approach. Berlin, Germany: Springer, 1997.

- [37] C. Papageorgiou and M. C. Smith, "Positive real synthesis using matrix inequalities for mechanical networks: Application to vehicle suspension," *IEEE Trans. Control Syst. Technol.*, vol. 14, no. 3, pp. 423–435, May 2006.

- [38] G. Tao and P. A. Ioannou, "Necessary and sufficient conditions for strictly positive real matrices," *IEE Proc. G - Circuits, Devices Syst.*, vol. 137, no. 5, pp. 360–366, Oct. 1990.

- [39] K. J. Åström and B. Wittenmark, Computer-Controlled Systems: Theory and Design. 3rd ed. Prentice Hall, Courier Corporation, NJ, USA, 1997.

**Carlos A. Villarreal-Hernadez** received the B.S. and M.Eng. degrees in electrical engineering from Tecnologico de Monterrey, Mexico, in 2015 and 2017, respectively.

He is currently working toward the Ph.D. degree in electrical engineering with Tecnologico de Monterrey, Monterrey, Mexico. His research interests include power electronics and energy conversion.

Omar Fernando Ruiz-Martinez received the B.S. and M.Eng. degrees in electrical engineering from Instituto Tecnologico de Ciudad Madero, Madero, Mexico, in 2005 and 2010, respectively and the Ph.D. degree in applied sciences of control and dynamic systems from Instituto Potosino de Investigacion Cientifica y Tecnologica, San Luis Potosi, Mexico, in 2017.

He is currently a Postdoctoral Assistant with Tecnologico de Monterrey, Campus Monterrey, Mexico. He is a member of the Sistema Na-

cional de Investigadores (level C), Mexico. His research interests include applied control to power electronics converters, electronics systems design, and energy conversion strategies.

Jonathan Carlos Mayo-Maldonado received the B.S. and M.Eng. degrees in electrical engineering from Instituto Tecnológico de Ciudad Madero, Madero, Mexico, in 2008 and 2010, respectively and the Ph.D. degree in electrical and electronic engineering from the University of Southampton, Southampton, U.K., in 2015.

He is currently an Associate Professor in electrical engineering with Tecnológico de Monterrey, Campus Monterrey, Mexico. His research

interests include system and control theory, power electronics and smart grid technologies.

Dr. Mayo-Maldonado was a recipient with the Doctoral Control & Automation Dissertation Prize 2015 by the Institute of Engineering and Technology (IET), for his thesis entitled *Switched Linear Differential Systems*, supervised by Dr. P. Rapisarda He is a member of the *Sistema Nacional de Investigadores (level 1)* in Mexico.

Jesus Elias Valdez-Resendiz received the B.S. and M.Eng. degrees in electrical engineering from Instituto Tecnológico de Ciudad Madero, Madero, Mexico, in 2009 and 2011, respectively. He received the Ph.D. degree in electronic engineering from the Centro Nacional de Investigacion y Desarrollo Tecnologico, Cuernavaca, Mexico, in 2015.

He is currently an Associate Professor in electrical engineering with Tecnológico de Monterrey, Campus Monterrey, Monterrey, Mexico. He

is member of the *Sistema Nacional de Investigadores* in Mexico. His research interests include power electronics, energy management, energy conversion and electric vehicles.

**Gerardo Escobar** (SM'08) received the Ph.D. degree in automatic control from the Signals and Systems Lab. LSS-SUPELEC, Université de Paris XI, France, in 1999.

From 2008 to 2012, he was a Principal Scientist with the Power Electronics Group, ABB Switzerland Ltd., Zurich, Switzerland. He is currently a Professor-Researcher with the School of Engineering and Sciences, Tecnologico de Monterrey, Nuevo Leon, Mexico. His main research interests include modeling, analysis, and

control design of power electronic systems, and their applications in renewable energy systems, power quality, grid integration, active filters, inverters, dc-dc converters, multilevel converters, batteries, electrical drives, wind power, photovoltaic systems; as well as nonlinear control design, adaptive control, repetitive control, and their applications in current control, voltage balance, grid synchronization and harmonic compensation, among others.

Dr. Escobar is a member of the National Research Fellows System level 3 (SNI-3), CONACyT, Mexico. He was an AE for the IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS from 2007 to 2016. He has been an Associate Editor (AE) for the IEEE TRANSACTIONS ON POWER ELECTRONICS since 2013.

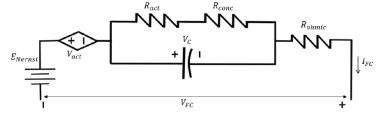

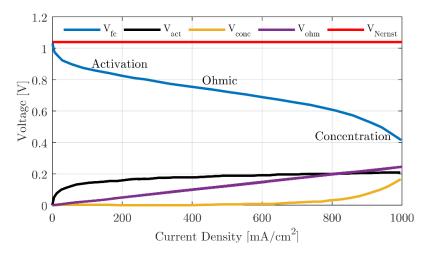

Julio C. Rosas-Caro received the B.S. degree in electronics and the M.S. degree in sciences in electrical engineering from the Instituto Tecnologico de Ciudad Madero, Madero, Mexico, in 2004 and 2005, respectively, and the Ph.D. degree in sciences in electrical engineering from the Cinvestav del IPN, Guadalajara, Mexico, in 2009.