INSTITUTO TECNOLÓGICO Y DE ESTUDIOS SUPERIORES DE MONTERRE

## VLSI ARCHITECTURES FOR A VIDEO CO-PROCESSOR TOWARD MOBILE APPLICATIONS BASED ON RECONFIGURABLE PLATFORMS.

TESIS QUE PARA OPTAR POR EL GRADO DE DOCTOR EN CIENCIAS DE INGENIERÍA **PRESENTA**

### FRANCISCO JAVIER ORTIZ CERECEDO

Asesor: Dr. ANDRÉS DAVID GARCÍA GARCÍA

Jurado: Dr. RENÉ ARMANDO CUMPLIDO PARRA,

> Dr. MIGUEL GONZÁLEZ MENDOZA, Secretario Dra. CLAUDIA FEREGRINO URIBE, Vocal Dr. JAIME MORA VARGAS, Vocal Dr. ANDRÉS DAVID GARCÍA GARCÍA Vocal

Presidente

Atizapán de Zaragoza, Edo. Méx., Noviembre de 2011.

### BIBLIOTECE

Tens TR 7871 FO. 7017

1

d

# INSTITUTO TECNOLÓGICO Y DE ESTUDIOS SUPERIORES DE MONTERREY CAMPUS ESTADO DE MÉXICO

# VLSI Architectures for a Video Co-Processor toward mobile applications based on reconfigurable platforms

DOCTORAL DISSERTATION

Presented by

## FRANCISCO JAVIER ORTIZ CERECEDO

To obtain the degree of

### DOCTOR IN ENGINEERING SCIENCES

Advisor: DR. ANDRÉS DAVID GARCÍA GARCÍA

Thesis Commitee: DR. RENÉ ARMANDO CUMPLIDO PARRA

DR. MIGUEL GONZÁLEZ MENDOZA DRA. CLAUDIA FEREGRINO URIBE

DR. JAIME MORA VARGAS

President Secretary Examiner Examiner

Atizapán de Zaragoza, Estado de México November, 2011

# Dedicatoria

A mis padres, Francisco y Reyna por su apoyo incondicional en todos los proyectos que he emprendido a lo largo de mi vida sin importar lo descabellados y complicados que éstos hayan parecido, sin su apoyo y sin su ejemplo no habría podido lograr nada, MUCHAS GRACIAS!

A mis hermanos Fernando e Hiram, gracias por estar conmigo en las buenas y en las malas, sin ustedes la vida sería muy aburrida.

# Agradecimientos

Quiero agradecer a mi director de tesis, Dr. Andrés García por su ayuda, sus consejos y sus valiosos comentarios que me ayudaron a llevar a cabo este trabajo de tesis.

Agradezco profundamente a los doctores René Cumplido, Claudia Feregrino, Miguel González y Jaime Mora por haberme hecho el honor de participar en el comité de evaluación de este trabajo.

Agradezco a todos mis compañeros del doctorado por el tiempo que hemos convivido y sobre todo por su amistad. Gracias Carmen, Diana, Aarón, Azzael, Danny, Jaime y Pedro.

Gracias al Tecnológico de Monterrey, Campus Estado de México por la beca que me fue otorgada para la realización de mis estudios de grado y por todas las facilidades prestadas durante mi estancia como estudiante.

Por último, quiero hacer un agradecimiento especial al Consejo Nacional de Ciencia y Tecnología (CONACYT) por la beca de manutención que me fue otorgada durante mis estudios doctorales.

## Resumen

El procesamiento de video es un campo que ha tenido un crecimiento notable en los últimos años, ha pasado de ser un área de investigación académica pura a ser un área de desarrollo para aplicaciones de seguridad y electrónica de consumo; actualmente hay una tendencia de mercado orientada a eliminar los reproductores ópticos para reemplazarlos con discos duros y así incrementar la capacidad de almacenamiento al mismo tiempo que se reducen los costos de operación. Un nicho de mercado emergente es el procesamiento de imágenes para aplicaciones médicas, en donde se requieren dispositivos especializados para auxiliar en el diagnóstico de enfermedades incluso si el médico se encuentra en otro lugar.

Un sistema de codificación de video requiere de varias etapas de procesamiento para adquirir, comprimir y codificar la información para después transmitirla a algún otro dispositivo o medio para su posterior reproducción. En términos computacionales, cada etapa es muy demandante, por lo que debemos escoger entre dos enfoques: hardware y software; las implementaciones en software son muy eficientes en términos del volumen de procesamiento de datos, pero el problema radica en que se desperdician recursos del sistema al estar ligados a una longitud de palabra fija dependiente de la arquitectura del procesador, adicionalmente, las operaciones de acceso y escritura a memoria tienden a disminuir el desempeño del sistema.

Cuando el volumen de procesamiento, el consumo de potencia y el desempeño son restricciones de diseño, los procesadores en hardware son la mejor opción para implementar tareas de codificación de video; existen varias arquitecturas de hardware apropiadas para la implementación de procesamiento de video como los Procesadores Digitales de Señales (DSP), Unidades de Procesamiento Gráfico (GPU), Arreglos de Compuertas Programables (FPGA) y Circuitos Integrados de Aplicación Específica. Cada uno de estos procesadores está especializado en tareas específicas, pero solo los FPGA han demostrado tener la capacidad de acelerar cualquier algoritmo o proceso debido a su alto grado de flexibilidad, permitiendo que el diseñador pruebe la arquitectura cuantas veces sean necesarias hasta lograr un diseño eficiente en términos de complejidad material, consumo de potencia y frecuencia de operación.

En la primera parte de esta tesis discutimos las características fundamentales de la representación numérica de la información visual y las bases de la compresión; los métodos de compresión con pérdida y sin pérdida son analizados y comparados; posteriormente se presenta un breve resumen de los estándares de codificación y al final de la sección se

presenta un comparativo entre los procesadores anteriormente mencionados.

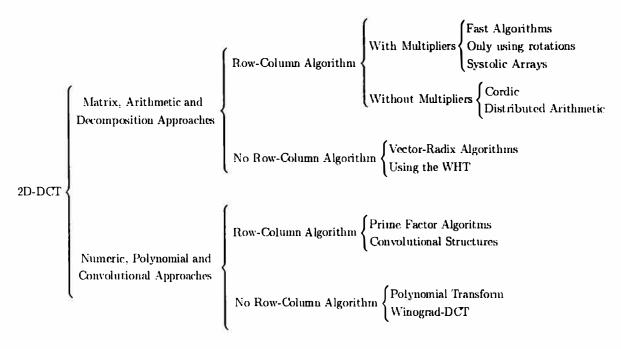

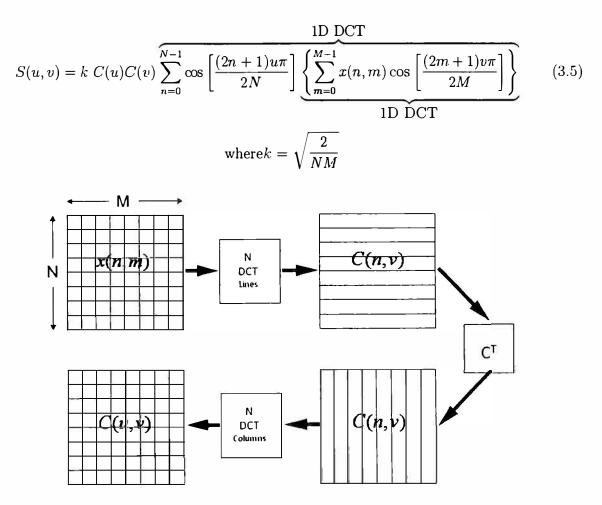

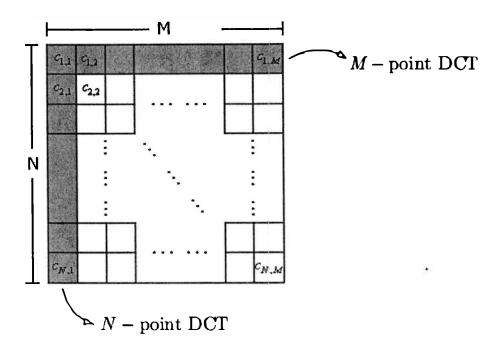

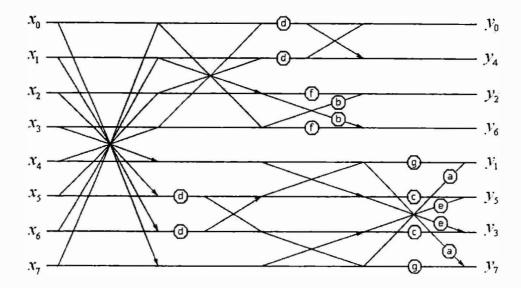

En la siguiente etapa de este trabajo se presenta un resumen de las arquitecturas de hardware utilizadas comúnmente para procesamiento de video; Las arquitecturas para calcular la Transformada de Coseno Discreta tienen la característica de ser regulares y apropiadas para la implementacin en alta escala de integración (VLSI); la mayoría de estas arquitecturas está basada en la descomposición Renglón-Columna que permite una implementación directa en hardware; los algoritmos rápidos se explican a profundidad, posteriormente se presenta un estudio de las arquitecturas basadas en Aritmética Distribuida y se establece un comparativo entre las dos familias en términos de la viabilidad para su implementación en FPGA.

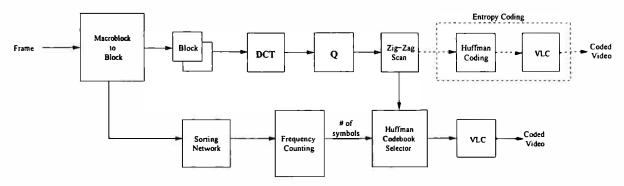

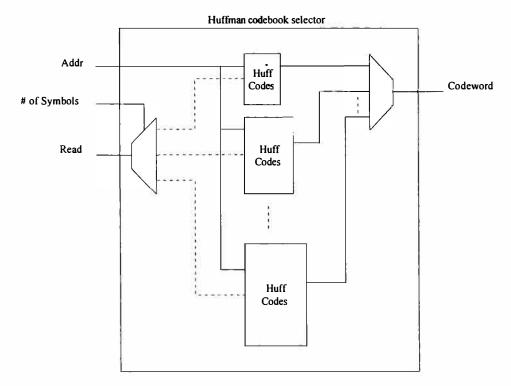

La codificación entrópica y la codificación de Huffman se explican en esta sección; existen varios esquemas para la codificación de Huffman que son apropiados para la implementación en ASIC, el problema principal radica en que son arquitecturas muy grandes que requieren de accesos constantes a memoria; posteriormente se explican los Algoritmos de Ordenamiento scrial y paralelo así como su implementación en hardware. Las arquitecturas paralelas permiten ordenar arreglos de datos en unos cuantos ciclos de reloj, por lo que se explora la posibilidad de estimar la función de densidad de probabilidad de la imagen con una red de ordenamiento. Al final de esta sección se presentan las arquitecturas para la Estimación de Movimiento.

En la siguiente etapa de este trabajo se presentan las implementaciones de los procesos requeridos para la codificación de video, se explica brevemente en qué consiste la adecuación algoritmo-arquitectura y se presentan los códigos de descripción material de los bloques aritméticos necesarios. Decidimos utilizar plataformas reconfigurables por sus características de flexibilidad y la posibilidad de probar diferentes configuraciones sin necesidad de cambiar completamente el diseño. En esta tesis se utiliza únicamente la librería ieee standard logic para reducir la utilización de recursos.

Finalmente, los resultados de las implementaciones arquitecturales son discutidos y comparados en términos de complejidad material, ya que si ésta es reducida, podemos suponer que habrá un consumo de potencia reducido. Se presentan algunos resultados de síntesis lógica y simulación para determinar la viabilidad de trasladar el sistema a un Circuito Integrado de Aplicación Específica.

# Abstract

Video processing has been a fast growing field in the recent years, it has evolved from a purely academic research area to a research and development area for consumer electronics, medical and security applications; actually there is a market trend oriented to remove all optical media reproducers and replace them with hard drives to increase media storage and to reduce operation costs; an upcoming niche market is identified as medical image processing, where dedicated devices are required to help in the diagnosis of medical conditions even if the physician is in other geographic location.

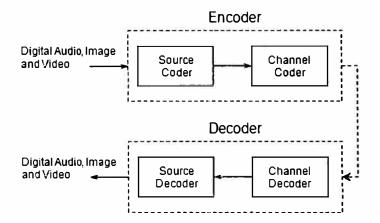

Conventionally a video coding system involves several processing stages to acquire, compress and code data to convey it efficiently to another media for a later reproduction. Each stage is very demanding in terms of computational complexity and oftenly we have to choose between a hardware or a software solution; software implementations of video coders are very efficients in terms of throughput, but they tend to underutilize the system resources as they work with fixed wordlengths and are tied to an specific processor architecture with external memory devices; read/write operations required to fetch data tend to diminish the system performance.

When system performance, power consumption and throughput are hard constraints a hardware processor is the best choice to implement video coding tasks; there are many hardware architectures suitable for implementing video processing like Digital Signal Processors (DSP), Graphic Processing Units (GPU), Field Programmable Gate Arrays (FPGA) and Application Specific Integrated Circuits (ASIC). Each processor is specialized for certain task, but only FPGAs have proven to be capable of accelerating any algorithm or process as they offer a high degree of flexibility, allowing the system designer to test the architecture over and over again until an efficient design in terms of material complexity, power consumption and maximum operating frequency is achieved.

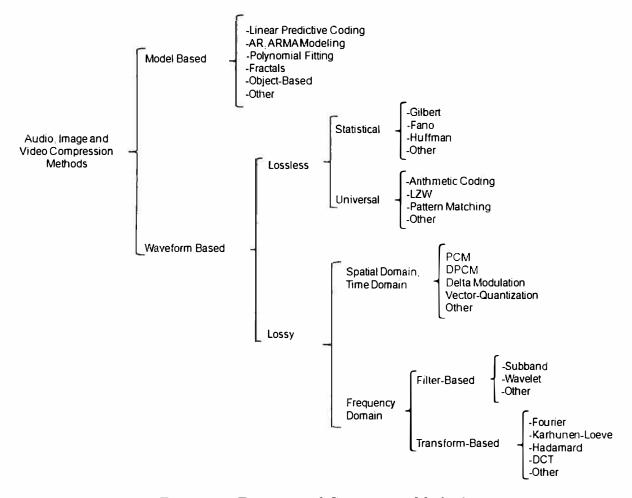

In the first part of this thesis we discuss the fundamental characteristics of the numerical representation of visual information and the necessity of compresion; both lossy and lossless compression methods are analyzed and compared; then a brief survey on video coding standards is presented, and a comparison between dedicated processors for image processing and their application is carried out.

In the next stage of this work, we survey hardware architectures for video processing tasks; Discrete Cosine Transform (DCT) architectures have the characteristic of being highly regular and suitable for Very Large Scale of Integration (VLSI) implementation, most of them are based in a Row-Column decomposition that allows to implement the algorithm directly in hardware; Fast algorithms are thoroughly explained, later, Distributed arithmetic architectures are studied and compared to fast algorithms in terms of the feasibility for FPGA implementation.

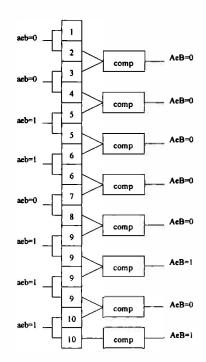

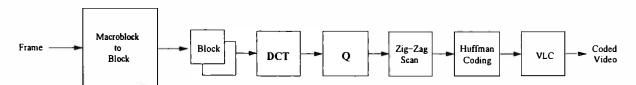

Entropy coding is explained along with Huffman Codes, some variable length coding architectures are surveyed and explained in terms of their material complexity, there are many Huffman Coding Schemes that are suitable for ASIC implementation, the main drawback is that all of them are too large and require external memories to store the code words; next we explain Sorting algorithms; this architectures are useful to sort ascendingly or descendingly arrays of numbers in a few clock cycles, there are two families of sorters, parallel and serial, in the former a random array is sorted in a comparison-exchange network, meanwhile in the latter the incoming value is inserted into the corresponding position of the array, in any case, we study the possibility of estimating the probability density function of the image with a sorting network, at the end of this section Motion Estimation architectures are presented and the representative block searching algorithms and hierarchical search algorithms are explained in detail.

In the next part of this work the architectural implementations of the above mentioned processes is presented, algorithm-architecture adequations are discussed and the HDL coding process of the required arithmetic modules is explained; we decided to work over reconfigurable platforms because they are the best developing tools because of their characteristics of flexibility and testability; FPGAs were the chosen platform to target HDL designs. Only ieee standard logic library was employed to code the architectures, eventhough there are IP cores and libraries that have many functions or blocks already build we decided to implement the algorithms directly into hardware to reduce resource utilization.

Finally, the results of the architectural implementations are discussed and compared in terms of material complexity, if the complexity is low, then we can expect a low power consumption, nevertheless sinthesis and simulation results are presented in order to determine the feasibility to translate the system design to an ASIC.

# Contents

| Re | esum  | en      |                                                | v    |

|----|-------|---------|------------------------------------------------|------|

| A۱ | bstra | ct      | •                                              | vii  |

| Li | st of | Tables  | s                                              | xiii |

| Li | st of | Figure  | es                                             | xv   |

| 1  | Intr  | oducti  | ion                                            | 1    |

| 2  | Stat  | e of tl | he Art                                         | 5    |

|    | 2.1   | Image   | Processing                                     | . 5  |

|    | 2.2   | Comp    | ression                                        | . 9  |

|    |       | 2.2.1   | Lossless Compression                           | . 12 |

|    |       | 2.2.2   | Lossy Compression                              | . 14 |

|    |       | 2.2.3   | Considerations in Compression Method selection | , 15 |

|    | 2.3   | Video   | Standards                                      | 16   |

|    |       | 2.3.1   | H.120                                          | 16   |

|    |       | 2.3.2   | H.261                                          | . 17 |

|    |       | 2.3.3   | MPEG-1                                         | . 17 |

|    |       |         | 2.3.3.1 Hierarchy                              | . 18 |

|    |       |         | 2.3.3.2 Group of Pictures                      | 20   |

|    |       | 2.3.4   | MPEG-2                                         | . 21 |

|    |       |         | 2.3.4.1 Macroblock Structure                   | 22   |

|    |       |         | 2.3.4.2 Slice Structure                        | 22   |

|    |       |         | 2.3.4.3 Quantization                           | . 22 |

|    |       |         | 2.3.4.4 Calculated Motion Vectors              |      |

|    |       |         | 2.3.4.5 Profiles and Levels of MPEG-2          | 23   |

|    |       |         | 2.3.4.6 Tools for Interlacing                  | . 25 |

|    |       | 2.3.5   | H.263                                          |      |

|    |       | 2.0.0   | 2.3.5.1 H.263+                                 | 25   |

|    |       | 2.3.6   | MPEG-4                                         | . 26 |

|    |       | 2.3.7   | H.264/AVC                                      |      |

|    | 2.4   |         | Processing Architectures                       | 28   |

### CONTENTS

|   |     | 2.4.1    | Hardwar    | e-Softwa     | are Ap  | plica | tion   | s   |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     |      | 1       |

|---|-----|----------|------------|--------------|---------|-------|--------|-----|------|------|----|-----|----|---------|---------------|------|------|-------|---------------|----|------|-----|-----|------|---------|

|   |     | 2.4.2    | Hardwar    | e-Softwa     | are Co- | Desi  | gn     |     | *    |      |    |     | ×  |         |               | × 1  | . :: | 0 %   | ×             | ěć |      | *:  | ٠   |      | 2       |

|   |     | 2.4.3    | Applicati  | ions         |         |       |        |     | *    |      |    |     | •  |         | s - 6:        |      |      | s :   | 22            | žγ | •    | •   | */  |      | 3       |

|   | 2.5 | Justific | cation     |              | 88 88   |       |        |     | •    |      | •  | • • | •  | ē /     |               | ٠    |      |       | •             | ÷1 | •    | •   | •   | . 3  | 6       |

| 3 | VLS | SI Arch  | nitecture  | es           |         |       |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     | 3    | 9       |

|   | 3.1 | Discret  | te Cosine  | Transfo      | rm .    |       |        |     |      |      |    |     | ·  |         | 97 <b>*</b> C |      |      | g: #1 | 75.0          |    |      | 200 |     | . 3  | 9       |

|   |     | 3.1.1    | 1D DCT     |              |         |       |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     |      | 2       |

|   |     |          | 3.1.1.1    | Fast al      |         |       |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     |      | 2       |

|   |     |          | 3.1.1.2    | Polyno       | _       |       |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     |      | 5       |

|   |     |          | 3.1.1.3    | Distrib      |         |       |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     |      | 6       |

|   |     | 3.1.2    | Memory     |              |         |       |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     |      | 3       |

|   | 3.2 |          | y Coding   | <del>-</del> |         |       |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     |      | 7       |

|   | 5.2 | 3.2.1    | Huffman    |              |         |       |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     |      | 8       |

|   |     | 0.2.1    | 3.2.1.1    | Known        |         |       |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     |      | ,<br>54 |

|   | 3.3 | Sorting  | g Algorith |              | _       |       |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     |      | 59      |

|   | 0.0 | 3.3.1    | Sorting 1  |              |         |       |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     |      | '2      |

|   |     | 0.0.1    | 3.3.1.1    | Proces       |         |       |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     |      | 2<br>'2 |

|   |     |          | 3.3.1.2    | Bubble       |         |       |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     |      | 2<br>'2 |

|   |     |          | 3.3.1.3    | Even-C       |         |       |        |     |      |      | •  |     | •  | •       |               |      | •    |       | ::00          | •  | •    |     | •   |      | '3      |

|   |     |          | 3.3.1.4    | Bitonio      |         | -     |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     |      | '9      |

|   |     | 3.3.2    | Serial So  |              | •       | _     |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     |      | 9<br>1  |

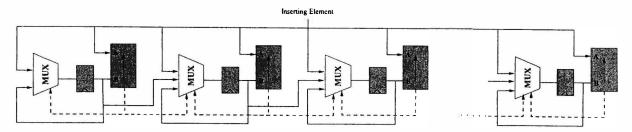

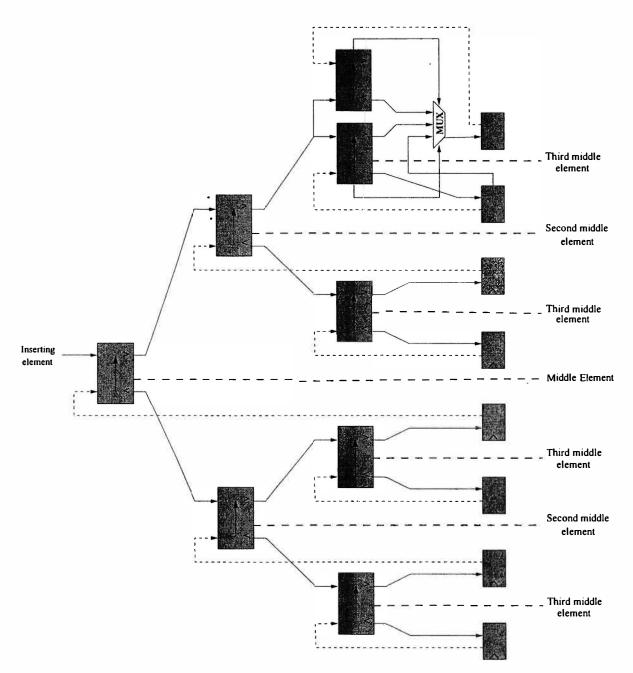

|   |     | 0.0.2    | 3.3.2.1    | Insertic     |         |       |        |     | •    |      | •  |     | •  | •       |               |      | •    |       | 5040-0        | 2  |      | •   | *** |      | 33      |

|   |     |          | 3.3.2.2    | Paralle      | _       |       |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     |      | 34      |

|   |     |          | 3.3.2.3    | Dichot       |         |       |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     |      | 34      |

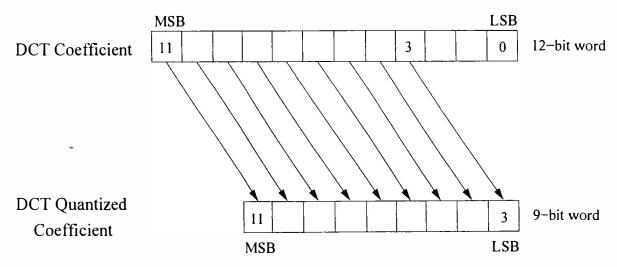

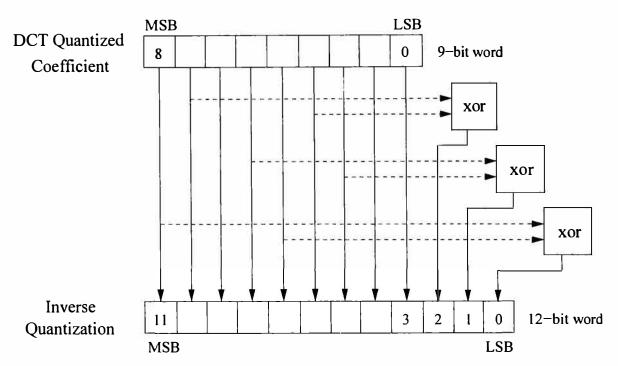

|   | 3.4 | Ought    | izer       |              |         |       |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     |      | 5<br>5  |

|   | 3.5 | •        | tor        |              |         |       |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     |      | 37      |

|   | 3.3 | 3.5.1    | Full Sear  |              |         |       |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     |      | 90      |

|   |     | 3.5.2    |            |              |         |       |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     |      | )2      |

|   |     | 3.5.2    | Hierarch   |              | •       | _     |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     |      |         |

|   |     | 3.3.3    | Known I    | mpieme       | entatio | ns ,  | æ 5∗ 1 | * * | i• i |      |    | • • | ×. | ::e:::: | e •           | * :  | •    | e 19  | (( <b>*</b> ) | ٠  | 7.8  | 65  | *   | . 9  | 93      |

| 4 | Arc |          | ıral Impl  |              |         |       |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     | 9    |         |

|   | 4.1 | Discre   | te Cosine  |              |         |       |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     | _    | 7       |

|   |     | 4.1.1    | Fast Alg   |              |         |       |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     |      | 7       |

|   |     |          | 4.1.1.1    | Multip       |         |       |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     |      | 8       |

|   |     |          | 4.1.1.2    | Cordic       |         |       |        |     |      |      |    |     |    |         |               |      |      |       | 7             | 12 | 85   | ¥.  | 4   | . 10 | 1       |

|   |     | 4.1.2    | Distribut  | ted Arit     | hmetic  |       |        |     | *    |      |    |     | >÷ |         |               |      | *:   |       |               |    |      |     |     | 10   | )3      |

|   |     | 4.1.3    | Memory     | Transp       | osition | 5 5   |        | 5 5 |      |      |    |     |    | U.S.O.  |               | 38 7 | **   |       | •             | ٠  | et i | •   | •   | . 10 | 17      |

|   | 4.2 | Entrop   | y Coding   |              |         |       |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     |      | )8      |

|   |     | 4.2.1    | Sorting A  |              |         |       |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     |      | )8      |

|   |     | 4.2.2    | Huffman    | Coding       | ζ       |       | 3 5    |     |      | 2. 5 |    | b : |    | 050     |               |      | 355  |       | -53           |    | •    | •   | •   | , 11 | . 2     |

|   | 4.3 | Coder    | Proposed   |              |         |       |        |     |      |      |    |     |    |         |               |      |      |       |               |    |      |     |     | 11   | 4       |

|   | 4.4 | Conclu   | usions     |              |         | . n c | * 0    |     |      |      | 9. |     |    |         |               |      |      |       | *3            |    |      | •   |     | . 11 | 7       |

| 5  | Res   | ults    |                            | 119   |

|----|-------|---------|----------------------------|-------|

|    | 5.1   | Discre  | ete Cosine Transform       | . 119 |

|    |       | 5.1.1   | Fast Algorithm             | . 119 |

|    |       | 5.1.2   | Distributed Arithmetic     |       |

|    |       | 5.1.3   | DCT Architectures Compared | . 123 |

|    | 5.2   |         | opy Coding                 |       |

|    |       |         | Sorting Algorithms         |       |

|    | 5.3   | Concl   | lusions                    | 126   |

| 6  | Con   | ıclusio | ons                        | 129   |

|    | 6.1   | Future  | re Work                    | . 130 |

| Bi | bliog | raphy   | v                          | 131   |

٠

# List of Tables

| 0.1  | Applications for Audio Income and Video Communication               | 10  |

|------|---------------------------------------------------------------------|-----|

| 2.1  | Applications for Audio, Image and Video Compression                 | 10  |

| 2.2  | Entropy Coding with Variable Length Symbols                         | 13  |

| 2.3  | Video Coding Standards Summary                                      | 16  |

| 2.4  | MPEG-1 Limitations                                                  | 18  |

| 2.5  | MPEG-2 Profile limits                                               | 24  |

| 2.6  | MPEG-2 Levels                                                       | 24  |

| 2.7  | Comparison between FPGAs, ASICs, GPUs, DSPs and CPUs                | 29  |

| 2.8  | Tasks in Platform-Based Design                                      | 34  |

| 3.1  | ROM content for $N=4$                                               | 50  |

| 3.2  | Contents of the reduced size ROM with OBC coding for $N = 4$        | 52  |

| 3.3  | VLC encoder operation                                               | 60  |

| 3.4  | VLC decoder operation                                               | 64  |

| 3.5  | Quantization                                                        | 87  |

| 3.6  | Parameters for simplified hierarchical block matching algorithm     | 94  |

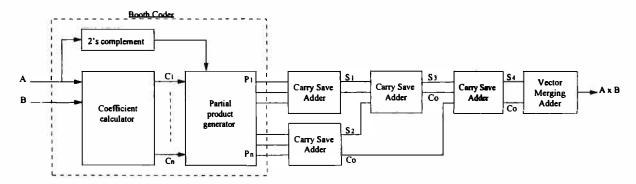

| 4.1  | Booth Coefficients                                                  | 99  |

| 4.2  | Frequency Counting Adder                                            | 113 |

| 5.1  | Cordic Synthesis Results                                            | 120 |

| 5.2  | 1D-DCT Fast Algorithm Synthesis Results                             | 120 |

| 5.3  | Shift-Accumulator Unit for DCT-DA                                   | 121 |

| 5.4  | 1D-DCT with conventional Distributed Arithmetic                     | 123 |

| 5.5  | 1D-DCT with Offset Binary Coding                                    | 123 |

| 5.6  | DCT-1D architectures synthesis results for Altera Cyclone II device | 123 |

| 5.7  | Compare-Exchange Synthesis Results                                  | 124 |

| 5.8  | 4-item merging network synthesis                                    | 124 |

| 5.9  | Merging Networks synthesis comparison                               | 125 |

| 5.10 | Sorting Networks synthesis comparison                               | 125 |

|      | Sorting Networks synthesis comparison                               | 126 |

|      | 32-item Pipelined Sorting Network                                   | 126 |

|      | -                                                                   |     |

# List of Figures

| 2.1  | Finite size window                                         |

|------|------------------------------------------------------------|

| 2.2  | Pixel Sampling Points                                      |

| 2.3  | Sampling and Reconstruction sequence                       |

| 2.4  | Generic compression system                                 |

| 2.5  | Taxonomy of Compression Methods                            |

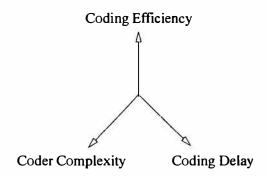

| 2.6  | Lossless Compression Tradeoffs 14                          |

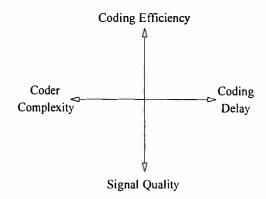

| 2.7  | Lossy Compression Tradeoffs                                |

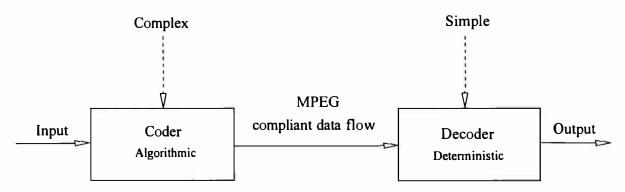

| 2.8  | Asymmetric Compression System                              |

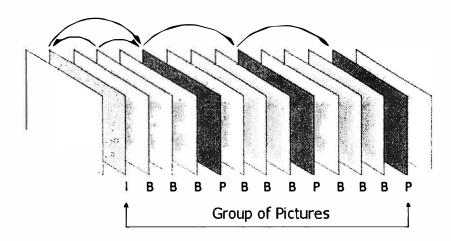

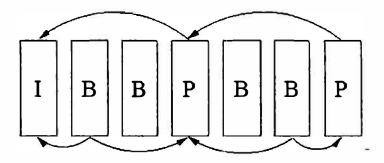

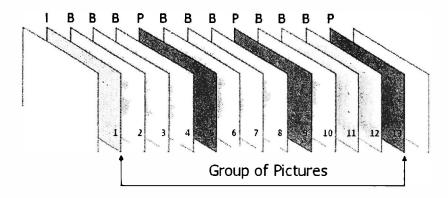

| 2.9  | Group of Pictures                                          |

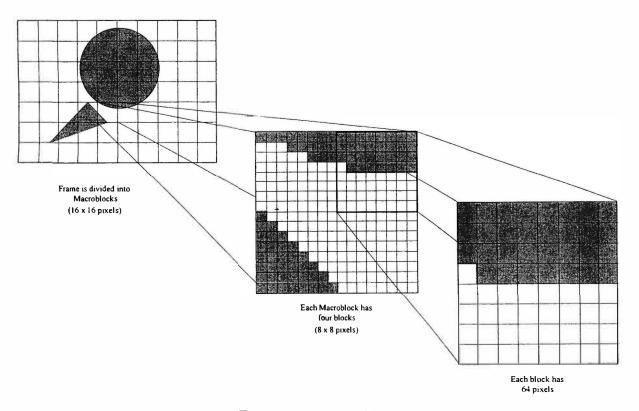

| 2.10 | Macroblock 19                                              |

| 2.11 | MPEG frames                                                |

| 2.12 | Group of Pictures deployment                               |

| 2.13 | Transmission of a GOP                                      |

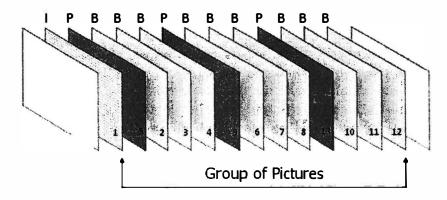

| 2.14 | MPEG-2 Macroblocks and sample positions 23                 |

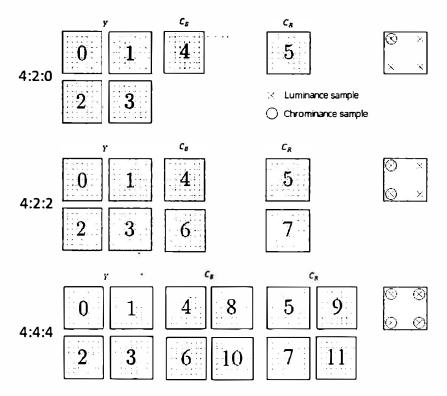

| 2.15 | Time to market ASIC vs. FPGA                               |

| 3.1  | DCT Architectures Classification 40                        |

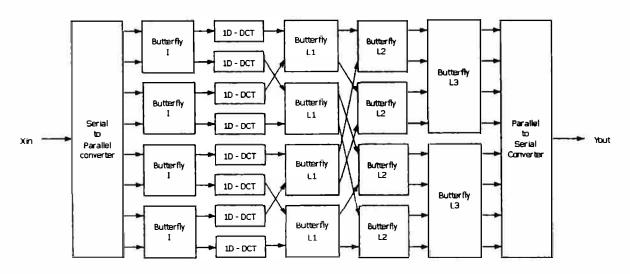

| 3.2  | DCT-2D General Architecture                                |

| 3.3  | DCTs required for an $M \times N$ image                    |

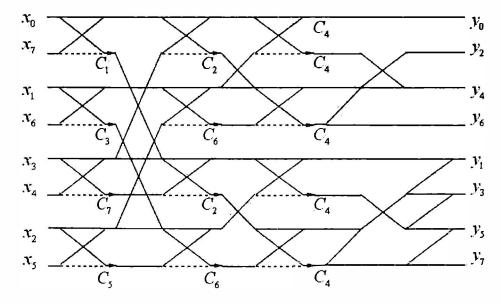

| 3.4  | Chen's Graph                                               |

| 3.5  | Lee's Graph                                                |

| 3.6  | Loeffler's Graph                                           |

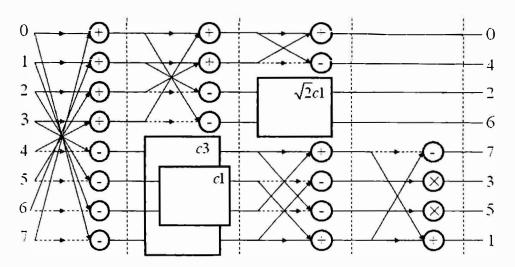

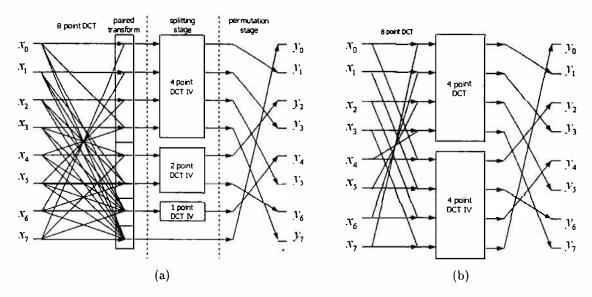

| 3.7  | 2D-DCT by Polinomial Transform                             |

| 3.8  | 8-point DCT II decomposition                               |

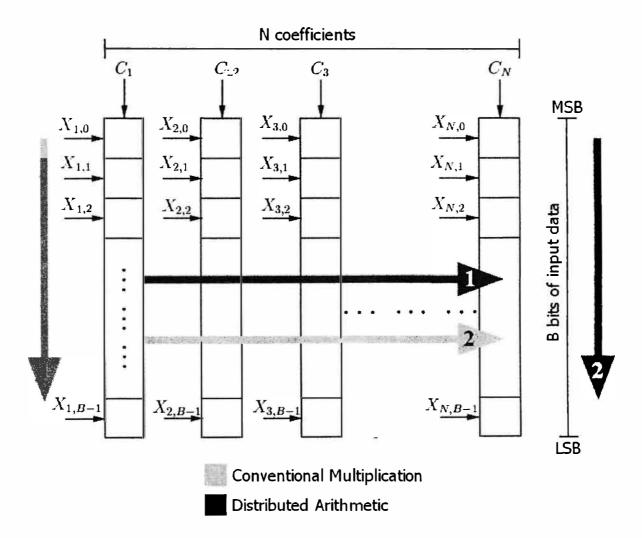

| 3.9  | Conventional Multiplication vs Distributed Arithmetic 49   |

| 3.10 | ROM-Accumulator Architectures                              |

|      | Distributed Arithmetic with Offset Binary Coding           |

|      | Pure Distributed Arithmetic Implementation of DCT          |

|      | Distributed Arithmetic with OBC Implementation of DCT . 55 |

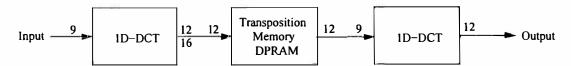

|      | Memory Transposition for DCT                               |

|      | Memory Transposing Architecture                            |

| 3.16 | Generic entropy coder 57                                   |

| 3.17 | Huffman Coding 59                                          |

### LIST OF FIGURES

| 2 10 | VLC Encoder                                       | 1          |

|------|---------------------------------------------------|------------|

|      |                                                   | 2          |

|      | VLC decoder                                       |            |

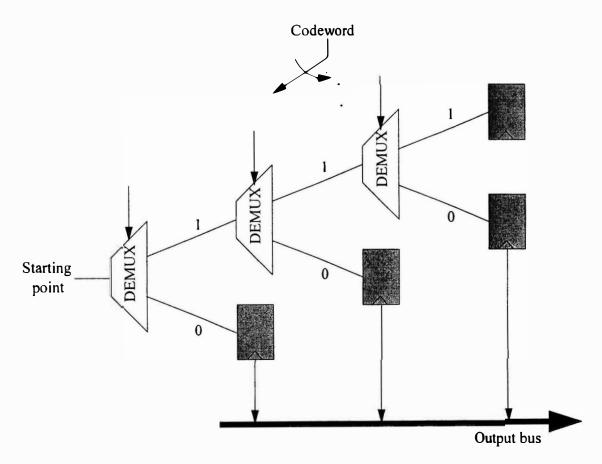

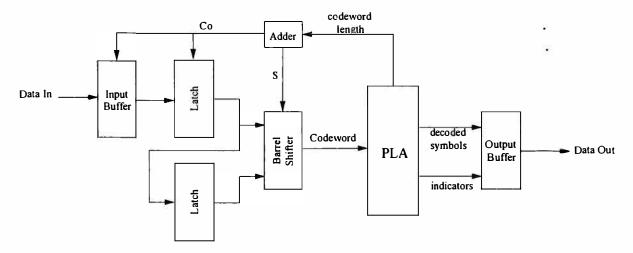

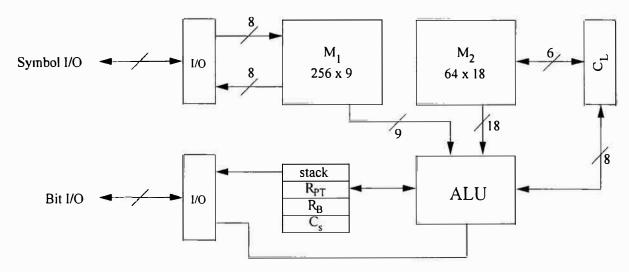

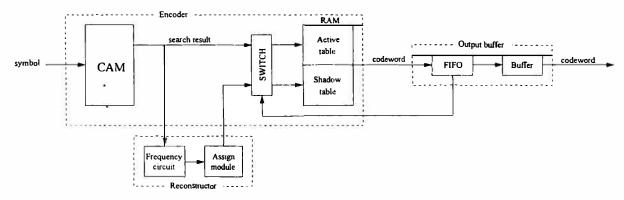

|      | Tree-Based architecture                           |            |

| •    | Variable I/O-rate architecture                    |            |

|      |                                                   |            |

|      |                                                   | 8          |

|      |                                                   |            |

|      | - O1                                              | 0          |

|      |                                                   | 1          |

|      | 1 0 ( )                                           | 2          |

|      |                                                   | '3         |

|      |                                                   | 4          |

|      | 0                                                 | <b>'</b> 5 |

|      |                                                   | 7          |

|      |                                                   | 8          |

| 3.33 |                                                   | <b>'</b> 8 |

|      |                                                   | <b>'</b> 9 |

| 3.35 | 32 item sorting network                           | 80         |

| 3.36 | 4 item bitonic sorting network                    | 31         |

| 3.37 | Iterative rule for Bitonic Merging Networks       | 32         |

| 3.38 | 8-item bitonic sorting network                    | 3          |

| 3.39 | Single insertion architecture for $N$ elements    | 3          |

| 3.40 | Cases of parallel insertion                       | 34         |

| 3.41 | Parallel insertion architecture                   | 35         |

|      |                                                   | 36         |

| 3.43 | Quantization Process                              | 37         |

|      | •                                                 | 88         |

|      |                                                   | 39         |

|      |                                                   | 1          |

|      |                                                   | 92         |

|      |                                                   | 93         |

| 0.10 |                                                   | _          |

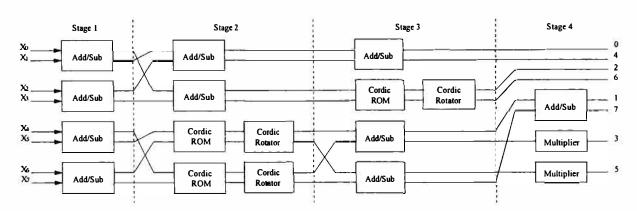

| 4.1  | 1-D DCT architecture                              | 98         |

| 4.2  | Booth Multiplier Architecture                     | )()        |

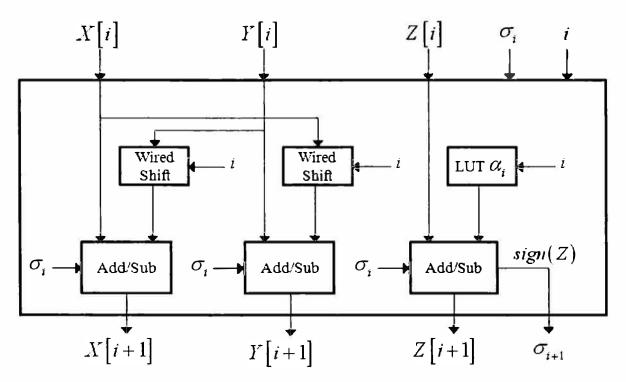

| 4.3  | Cordic Serial Architecture                        | )2         |

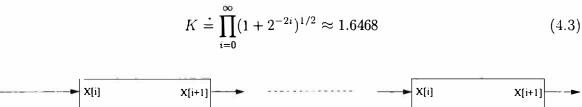

| 4.4  | Pipelined Cordic Architecture                     | )3         |

| 4.5  | Shift-Accumulator Unit                            | )4         |

| 4.6  | DCT- DA Finite State Machine                      | )5         |

| 4.7  | ROM-Accumulate Architecture                       | )6         |

| 4.8  | Shift-Accumulator unit for OBC                    |            |

| 4.9  | Row-Column Transformation architecture for 2D-DCT |            |

| 4.10 |                                                   |            |

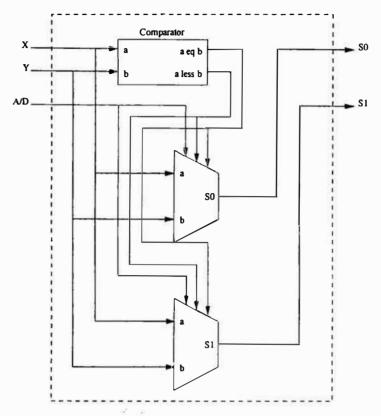

| 4.11 | Compare-Exchange module                           |            |

| 4.11 | Compare-Exchange module                           | JY         |

### LIST OF FIGURES

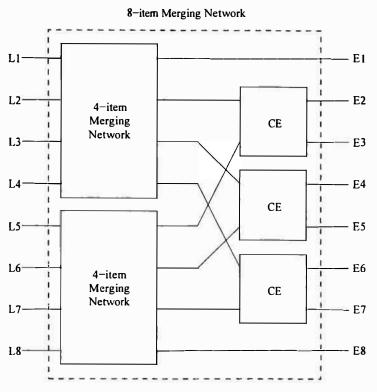

| 4.12 | 8-item Merging Network Architecture                     | 111 |

|------|---------------------------------------------------------|-----|

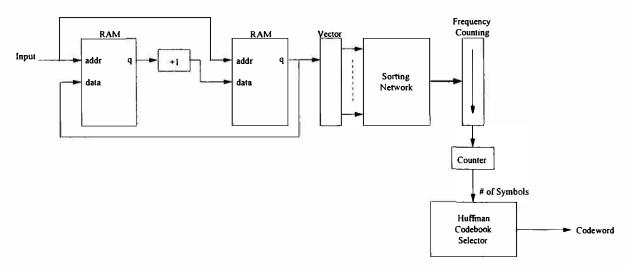

| 4.13 | Huffman Coder proposal                                  | 114 |

| 4.14 | Frequency Counting                                      | 115 |

| 4.15 | Video Compression System                                | 115 |

| 4.16 | Proposed Video Coder                                    | 115 |

| 4.17 | Huffman Codebook Selector                               | 116 |

| 4.18 | Sorting Network reduction for the proposed architecture | 117 |

| 5 1  | RTL view of Fast Algorithm                              | 191 |

|      |                                                         |     |

| 5.2  | RTL view of Distributed Arithmetic 1D-DCT               | 122 |

| 5.3  | RTL of a 32-item Sorting Network                        | 127 |

# Chapter 1

# Introduction

Image and Video Processing is a field that has changed exponentially through recent years; it is one of the most successful and used technologies and has evolved from an academic research area to a commercial application research and development area; nowadays is common to hear that certain device has real-time video processing capabilities, or that supports many image and video standards; why do we talk about real time processing? Is it really necessary? Why do we need to process such large amounts of data in short periods of time? Why are we so concerned about giving real time processing capabilities to consumer electronics?

Real-time image and video processing is one of the fastest growing technologies in the communications field as High Definition television, streaming and videoconferencing applications reach everyday larger markets, but also is of great importance in security surveillance systems for large facilities like airports, bus and train stations, schools and even state buildings, video processing is a critical tool for medical applications where an accurate visual representation of images is required to help physicians diagnose a number of diseases or medical conditions, video processing could also help monitoring patients with infectious diseases without endangering medical personnel.

To process an image or a sequence of images we must perform various processes consecutively to compress, quantize, code, and convey information to an storage device or to another processor that reverses the process; compression is understood as the process of eliminating information redundancies within a frame, as we know, there are some light components that the eye cannot see, therefore their presence within the image is irrelevant; if the information of the frame is highly correlated we can assume that there is more information than required, the same principle applies to consecutive frames where a pixel has a high probability of staying as it is in the next frame; The standardized image compression is achieved by applying a Fourier based orthogonal transform known as Discrete Cosine Transform, this transform has the characteristic of concentrating the energy in the lowest frequencies of the cosine function, letting the frame with a huge amount of irrelevant information that can be removed before sending data to the next process in the chain.

The quantization process consists of assigning binary values within a range to the DCT coefficients to that the next process, known as entropy coding can be performed easily and smoothly; unlike DCT, entropy coding is a lossless coding scheme that helps to reduce the amount of information that has to be stored or conveyed, the greatest challenge in entropy coding is to make efficient a computationally exhaustive method known as Huffman Coding. Finally, the most demanding task in terms of computational operations must be performed, Motion Estimation is a method used to identify the portions of the frame that change through adjacent frames, this process is required to increase the maximum DCT compression and to increase the maximum operating frequency.

Images and Video can be processed either in hardware or software, software video processing algorithms are very fast and accurate, but they rely on a computer processor, and an operating system to handle memory access and peripheral devices; hardware video processing can be performed by a number of specialized devices like DSPs, GPUs, FPGAs and ASICs; each signal processor is suitable for some task, for example DSPs are a good option if we need to compute filter functions of convolutional operations between vectors, regularly they are programmed in C language; GPUs are generic devices optimized for video processing tasks, they are very close to CPUs as they only have cache memory and require external memories with random accesses to store the code that is going to be executed, they are popular because they can be programmed with high level languages and their processing rate is usually high.

FPGAs represent along with ASICs the most efficient hardware option to process video; FPGAs have the advantage of being extremely flexible; as a designer, one can test an architecture over and over again until a satisfactory result is achieved, their configuration is usually coded in Hardware Description Languages like Very High Speed Integrated Circuits Hardware Description Language (VHDL) or Verilog HDL allowing the designer to code a complex system in a modular fashion, an FPGA is capable of performing any task of an ASIC, the main difference between them is that FPGAs need to be configured before the process starts and ASICs are already configured to perform an specific task and cannot be used for any other application.

1

This thesis is concerned with the design of a pure VLSI architecture of a video co-processor that does not rely on a CPU or external memory devices to compress video frames; most of video processing tasks are computationally exhaustive, therefore it is necessary to translate the algorithms into hardware to reduce the computational complexity employing parallel and pipelining techniques by accelerating the processes and reducing the critical path. VLSI design over reconfigurable platforms will allow us to compare hardware implementations targeted for power consumption, die area and operating frequency to establish a triple commitment between design constraints to find the optimum architecture.

The methodology of this thesis consisted in analyzing the algorithms of every video processing stage in the main layer, then a preliminary translation of algorithm to hardware is performed in order to begin testing the design constraints; after analyzing the algorithm's

computational complexity, a hardware version is coded in VHDL and then is synthesized with Altera Quartus II software to determine the material complexity, silicon area and maximum operating frequency of the module.

### Thesis Outline

This thesis is organized as follows. In Chapter 2 the basic concepts of image processing are explained and taken as the basis for compression; Lossy and Lossless compression methods are explained in detail and some recomendations for chosing a compression scheme were presented; A video coding standard survey is presented to understand the different processes that might be follower in order to process video in an efficient way, also a brief summary of video processing devices is presented, later in this chapter a comparative table between DSPs, CPUs, GPUs, FPGAs and ASICs is presented.

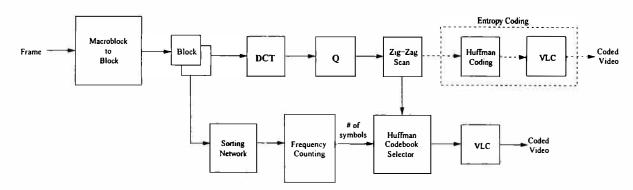

Chapter 3 presents a study of the available VLSI architectures for DCT, Quantization, Entropy Coding, Sorting Algorithms and Motion Estimation; the performance of each architecture is thoroughly discussed and a feasibility analysis between existing architectures for a determined processing stage is presented; at the end of the chapter a novel video coder is presented and compared to a generic coder in terms of the number of clock cycles required to process video through all the stages.

In chapter 4 is reported every architecture implemented in the FPGA in terms of how many logic elements are required, how many flip-flops and what amount of memory is required for the proposed architectures, we look forward establishing an approximate measure of the material complexity of the Co-Processor; Chapter 5 presents the results of the architecture synthesis for DCT and sorting networks, a comparison is made between synthesis results optimized for area and speed and the feasibility of implementation in a single reconfigurable device is studied.

Finally, concluding remarks are given and future work is highlited.

•

# Chapter 2

# State of the Art

In recent years there has been a significant evolution in algorithms and architectures for audio, image and video processing [1]. On the algorithm field robust methods for size reduction of audio, image and video data have been developed in order to make easier the data manipulation, storage and transmission; on the architecture field nowadays it is possible to implement complex compression processes on a relatively low cost integrated circuit, in fact this has incited a great deal of activity in developing multimedia systems for the consumer market [2].

The importance of these advancements is that audio, image and video information have the potential to become another data type, this implies that multimedia data can be digitally encoded so that it can be stored and transmitted in the same media or channel with other digital data types [3]. Data encoding standardization can lead the industry to the development of low cost implementation that will promote the generalized use of multimedia information [4].

### 2.1 Image Processing

Sight is one of the senses that allow us to perceive and assimilate an incredible amount of information in a short time interval [5], the variety of information that goes through the eye to be interpreted by the brain can be consider infinite as we never stop receiving visual information (unless of course we close our eyes). Throughout the years we have increased sight capability by creating devices capable to detect electromagnetic radiation even if the wavelengths are outside the normal vision range. By the use of sound waves or X-rays we are able to "see" inside objects and into locations far beyond our scope, high speed videocameras allow us to see the slightest details of a moving object like a flying humming bird.

Visual information is a term that cannot be accurately defined as it involves everything, there is no way to explain the term unless we introduce some restrictions; first of all, we

shall assume that information is enclosed in a finite image size, that is, the viewer receives the visual information as if looking through a rectangular window of finite dimensions as shown in figure 2.1<sup>1</sup>; every image or video capturing device works under the same principle of handling finite amounts of information. Second restriction is based on the assumption that the viewer does not have the capability of depth perception, so he cannot tell how distant objects are by changing the focus of his eyes, in exchange, he can infer whether the object is in the foreground or in the background based on the position of the object with respect to others.

Figure 2.1: Finite size window

Having these two restrictions in mind, visual information is determined by the wavelengths and light intensities that passes through each point of the window and reach the viewer eyes, hence, the problem of representing visual information in a numerical form is reduced as we only have to represent the intensity distribution of the finite size window. If a cartesian plane is imposed on the window we can represent the perceived intensity at any point (x, y). Thus I(x, y) represents the visual information or image at the instant of consideration, later we will add the parameter t for images that vary with time.

There are certain images I(x,y) that can be exactly specified, for example a light square over a dark background could be described as indicated in equation 2.1, the main problem is that no such exact specification is possible for real life situations with a limited amount of numerical data, hence an approximation of I must be done if it is to be processed in a practical system.

$$I(x,y) = \begin{cases} 1 & a \le x \le b, \ c \le y \le d \\ 0 & \text{otherwise} \end{cases}$$

(2.1)

1

As the majority of images must be stored, transmitted or processed a binary representation of data is required; I(x,y) must be represented by a finite number of bits, the main

<sup>&</sup>lt;sup>1</sup>Picture taken from www.bellasartes.gob.mx

problem relies in the wordlength that must be chosen; as we know, bit representation is an aproximation to the closest level of intensity, so, to increase the accuracy of the representation we must increase the number of bits per word; this decision must be seriously considered as it might lead to an increase in material complexity, making the system too expensive in terms of silicon area and can affect the maximum operating frequency and power consumption of the processor, so it is necessary to estimate the *minimum* representational fidelity required for the particular application to design the processing system accordingly [5].

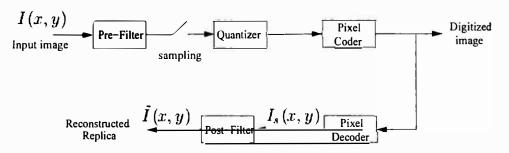

Deciding what degree of accuracy is needed in a system is not an easy task, starting with I(x,y) we must find a digitization scheme that comply with computational constraints and then construct the corresponding representation of data; from this data we must reconstruct an approximate replica  $\tilde{I}(x,y)$  of the original image. Next we must assume that a distortion measure  $D(I,\tilde{I}) \geq 0$  exists to indicate how accurate is  $\tilde{I}(x,y)$  with respect to I(x,y); although this coding issues are very specific, there are several difficulties associated to it, first of all, image processing systems are designed to handle a variety of image formats, this leads to different distortion measurements per format, so it could be possible to have image with high distortion for all coding schemes, thus making impractical to work with. The next problem is that the distortion measure can be out of the desireable constraints making the system unfeasible; even though this issues need to be considered, there are other aspects that can be used to evaluate a coding system like the complexity, robustness, resilience, compatibility and scalability [6].

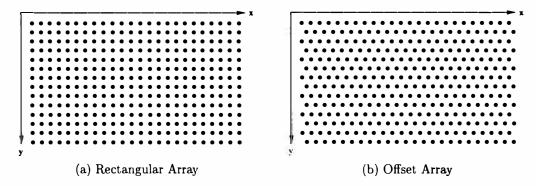

Now that is clear that we cannot describe I(x,y) with absolute accuracy it is evident that we require a finite number of bits to represent the intensity levels of I with an acceptable degree of accuracy; if time is considered as a parameter, then the whole process of sampling and quantizing is performed in a repeating cycle known as PCM coding; the set of sampling points of the image can be considered as a bidimensional array where samples are placed both on vertical and horizontal directions as shown in figure 2.2a, a slight variation of the sampling array is shown in figure 2.2b, notice that some rows are shifted by half sampling period; this samples are commonly known as picture elemets or **pixels**, in this way, pixel(x,y) is exactly the same than I(x,y).

Pixels should be located close together to measure the intensity variations of the area of interest, but, if we locate them too close we will have an unnecessary amount of information, so, the required sampling density depends on the intensity variations that the processor must accomodate, this sampling density is closely related to resolution; there are some techniques to measure resolution, one is the minimum distance between two lines or two pixels within the image, another metric is related to frequency contents of the image, this is especially useful when working with Fourier transform of any other Fourier related orthogonal transform; keeping this in mind, we can say that sampling density is chosen depending on either resolution or processing costs.

Once the sampling density has been determined, there might be some fast variations in

Figure 2.2: Pixel Sampling Points

the intensity levels within pixel(x,y) making difficult to measure accurately with the selected sampling rate, this happens often when optical devices have a larger resolution than needed, this fast transitions tend to distort the visual information, having as a result an image that does not represent the real data; in signal processing this phenomenon is known as pre-alias. To prevent this effect we require to take an average of samples surrounding each (x,y) pixel; even if intensity transitions are too fast or too small they would not change the final representation of visual information.

An easy method is to form a weighted average over the pixel neighborhood; for this we need a weighting function  $h_c(u, v)$  that peaks only at (0,0) and falls in any other case, the average or filtered image is then expressed as shown in equation 2.2; I(w, z) is calculated as the instantaneous value at pixel (w,z) (see 2.3. The intensity at each point of the image is replaced by a weighted average, this process is known as pre-filtering since I has not been sampled.

$$\bar{I}(x,y) = \int_{y-\delta}^{y+\delta} \int_{x-\delta}^{x+\delta} I(w,z) h_c(x-w,y-z) dwdz$$

(2.2)

$$I(w,z) = \delta(w)\delta(z) \tag{2.3}$$

Pre-filtering helps to reduce the amount of information as only a finite number of samples is represented, fast variations of intensity are removed and intensity values are quentized to finite accuracy. Having the quantized pixels of the filtered image we might need to reconstruct a replica  $\tilde{I}(x,y)$  of the original image, the main problem is deciding what intensity values are going to be assigned at (x,y) points that do not correspond to a sampling point; we might choose either to assign a zero or a near value; in both cases an artificial pattern will appear in  $\tilde{I}(x,y)$  causing a post-aliasing effect, this problem can be diminished if we interpolate between pixels to obtain smooth intensity transitions. Let  $h_d(u,v)$  be an interpolation function, so that the reconstructed replica is given by equation 2.4, if the sampled replica is defined using

Dirac delta functions, then equation 2.4 can be re-written as shown in equation 2.5 and the reconstructed image is given by equation 2.6, the sequence of sampling and reconstruction of an image is shown in figure 2.3.

$$\tilde{I}(x,y) = \sum_{k} \bar{I}(x_k, y_k) h_d(x - x_k, y - y_k)$$

(2.4)

$$I_s(x,y) = \sum_{k=1}^{N} \bar{I}(x_k, y_k) \delta(x - x_k) \delta(y - y_k)$$

(2.5)

$$\tilde{I}(x,y) = \int \int I_s(w,z)h_d(x-w,y-z)dwdz$$

(2.6)

Figure 2.3: Sampling and Reconstruction sequence

## 2.2 Compression

Compression is a process intended to produce a compact digital representation of a signal [2] [3]; when the signal is defined as a video stream or an audio segment the real problem of compression is to minimize the bit rate of the digital representation; it is important to state that without compression, many applications would not be feasible as shown in table 2.1.

Audio, Image and Video signals have repeated or irrelevant information known as redundant data. If we define b and b' as the number of bits in two different representations of the same information, then we can define C as the  $Compression\ Ratio$

$$C = \frac{b}{b'} \tag{2.7}$$

And from the compression ratio we can calculate the relative redundancy of data:

$$R = 1 - \frac{1}{C} \tag{2.8}$$

If we consider a compression ratio C = 10 (10:1), means that 10 bits of data can be represented using one single bit in compressed form, when we calculate the relative redundancy of data R = 0.9, we notice that 90% of data is redundant and can be removed.

| Application                              | Uncompressed Data Rate | Compressed Data Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Voice                                    | 64 Kbps                | 2 – 4 Kbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 8 ksamples/s, 8 bits/sample              |                        | 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 1000 - 10 |

| Audio conference                         | 128 Kbps               | 6 - 64 Kbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 8 ksamples/s, 16 bits/sample             |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Video conference (15 fps)                | 30.41 Mbps             | 64 – 768 Kbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| framesize 352 × 240, 24 bits/pixel       |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Digital audio                            | 1.5 Mbps               | 128 - 768 Kbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 44.1 ksamples/s, 16 bits/sample          |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

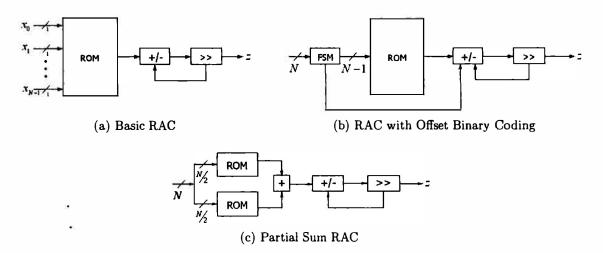

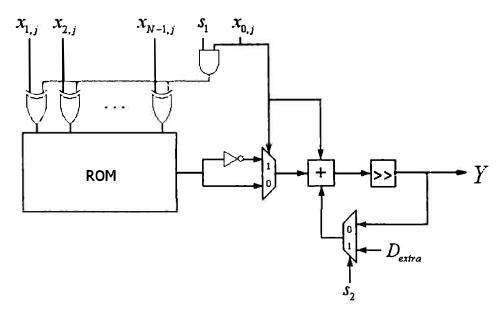

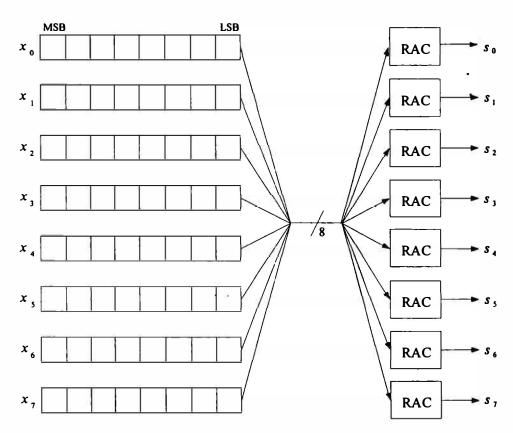

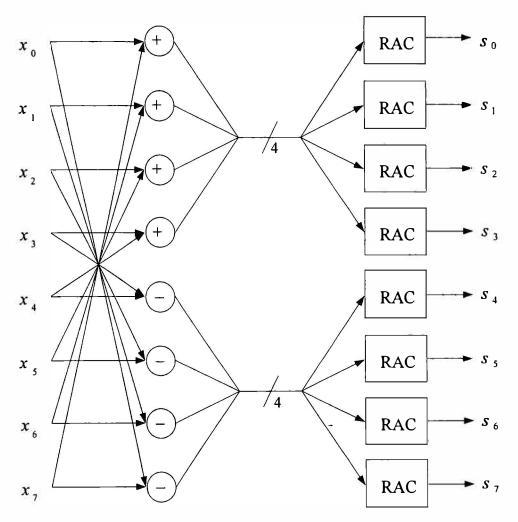

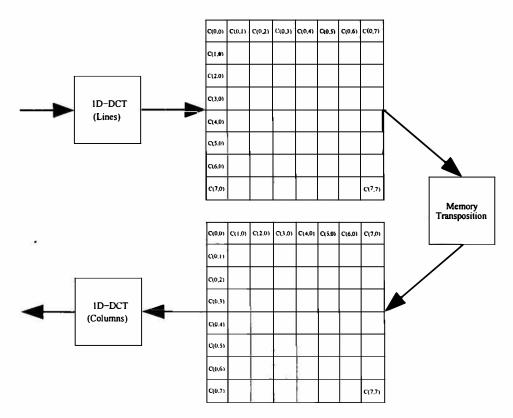

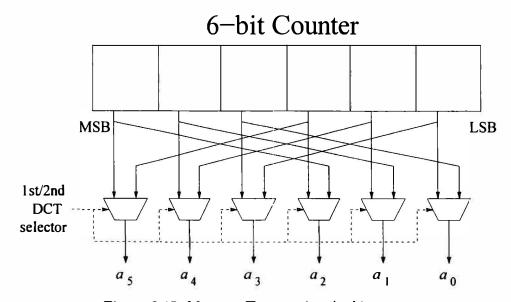

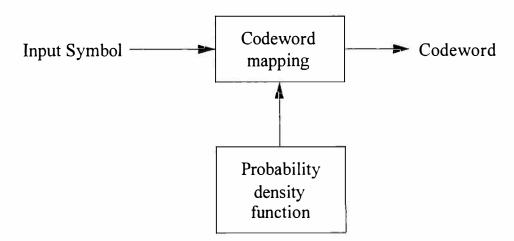

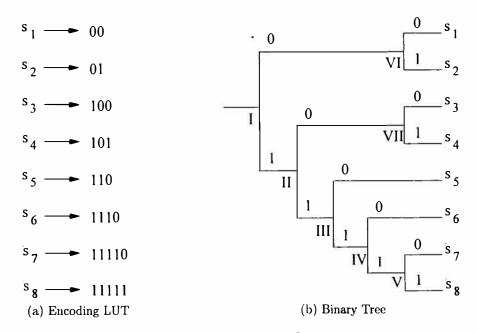

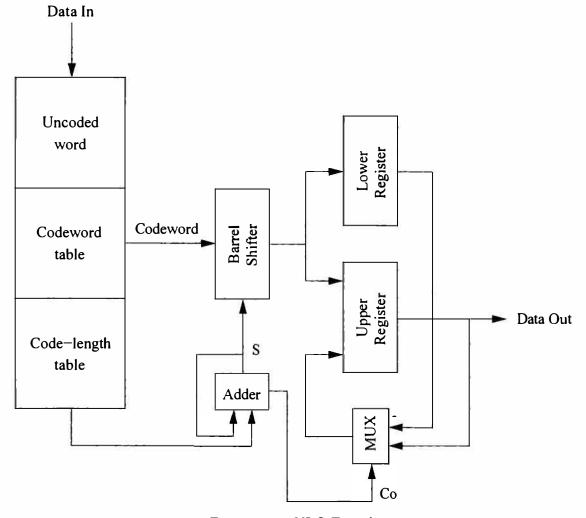

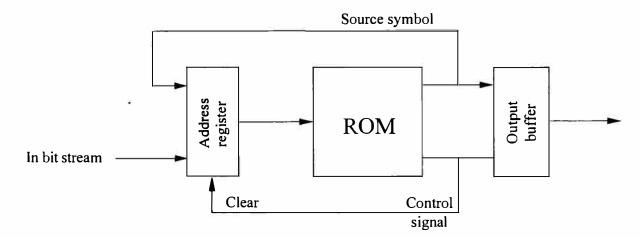

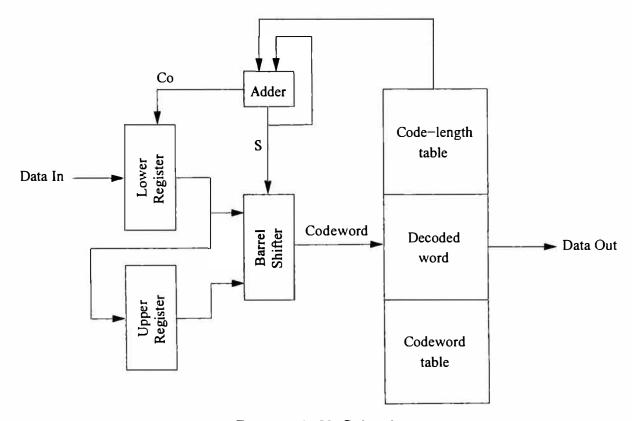

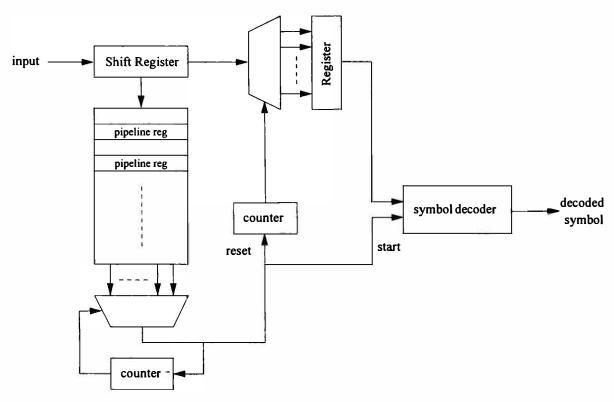

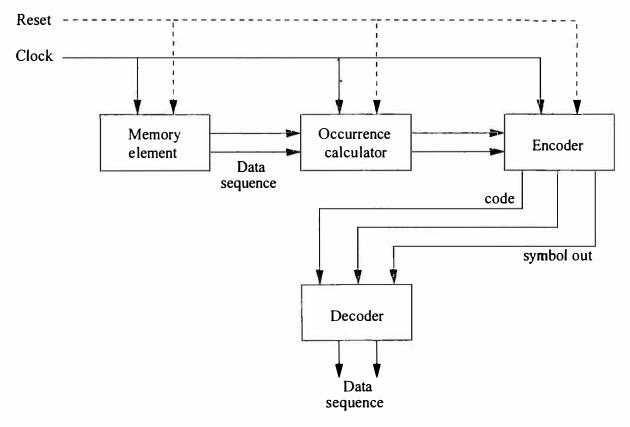

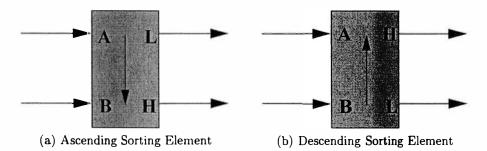

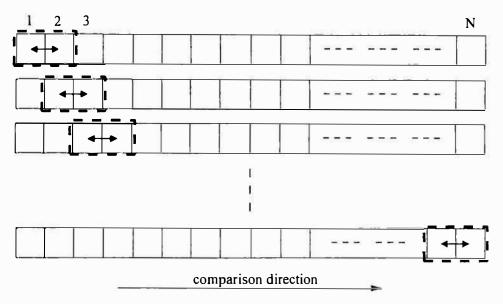

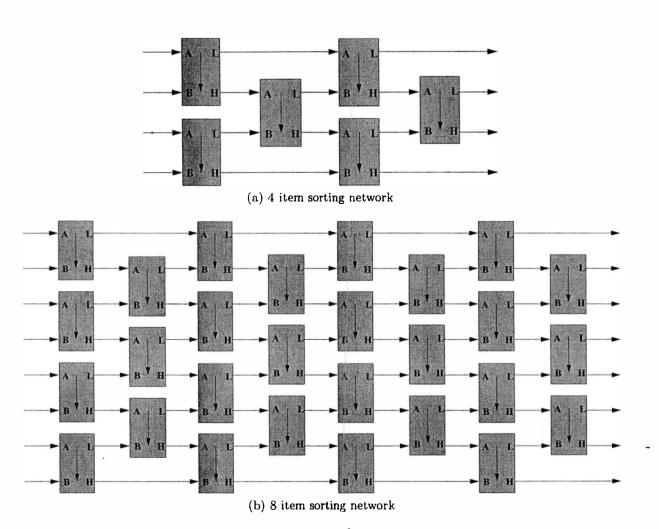

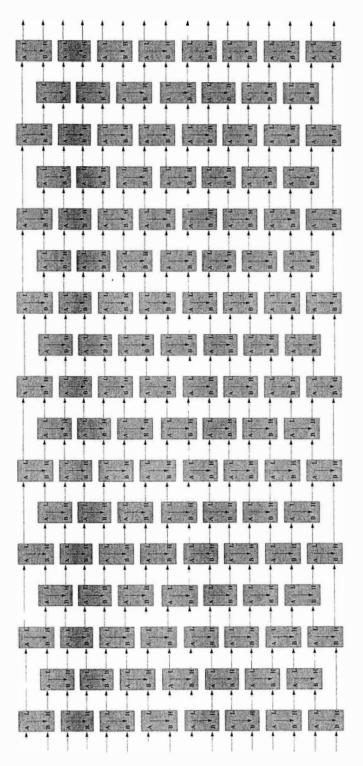

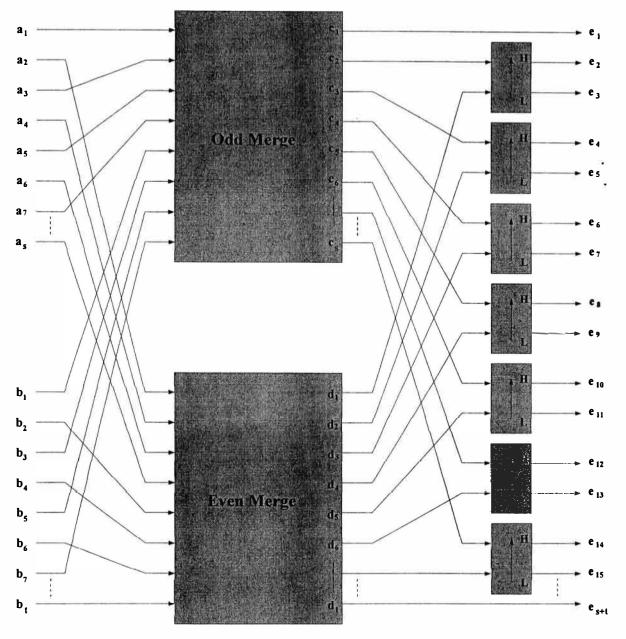

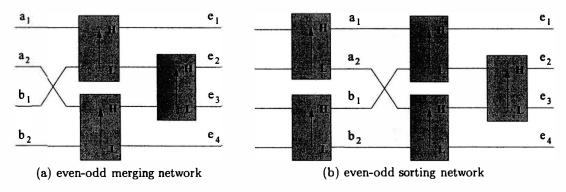

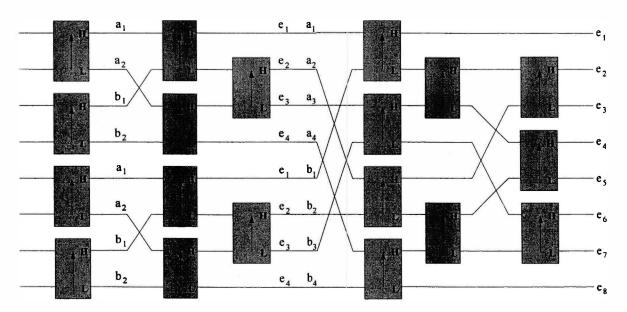

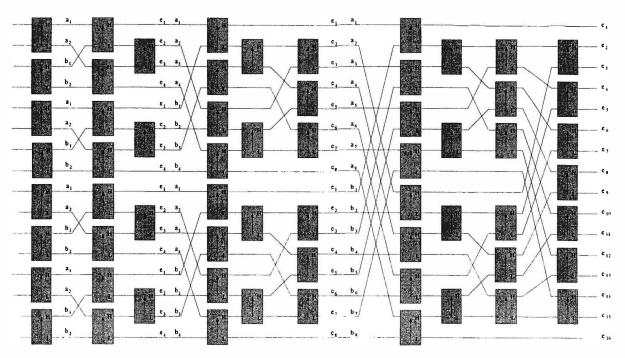

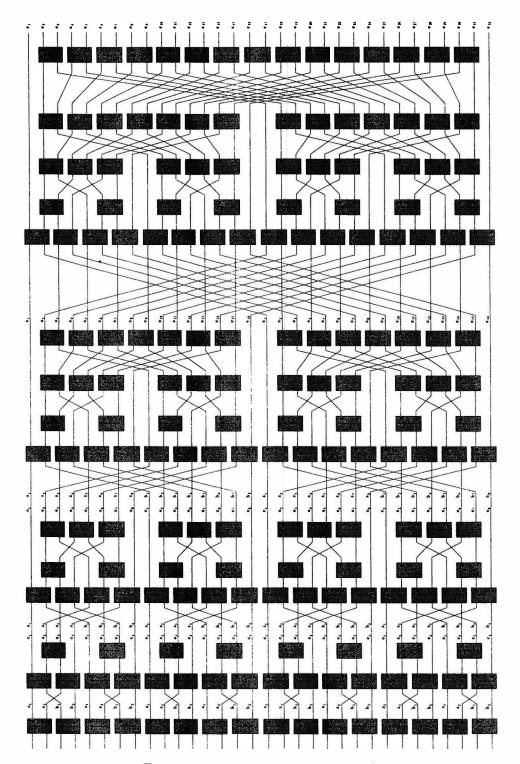

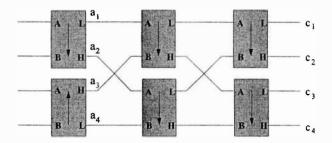

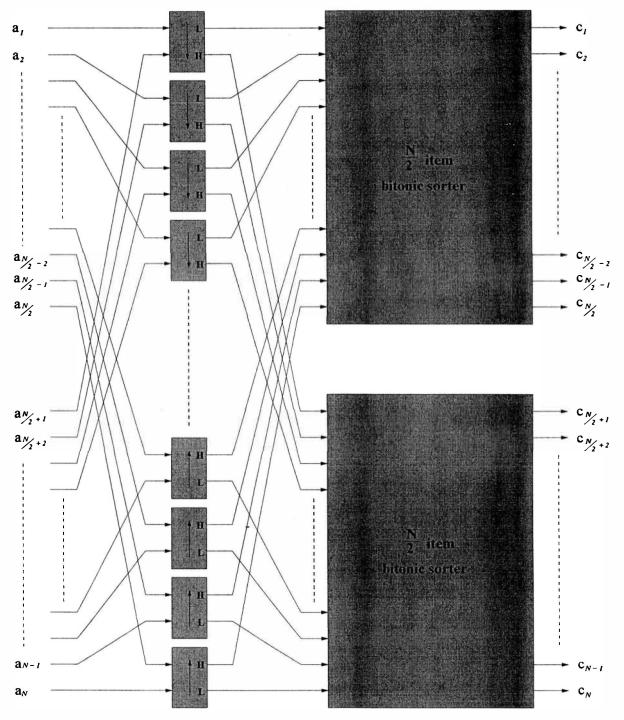

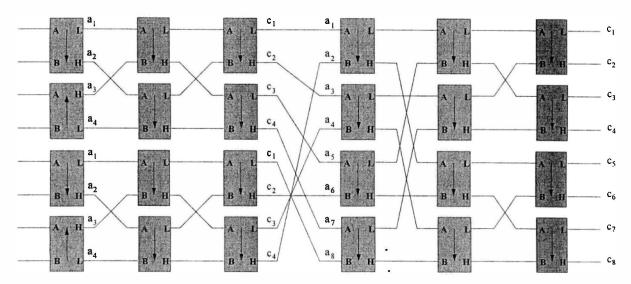

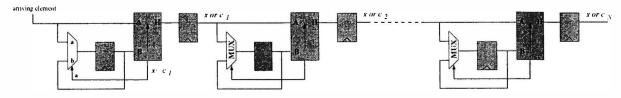

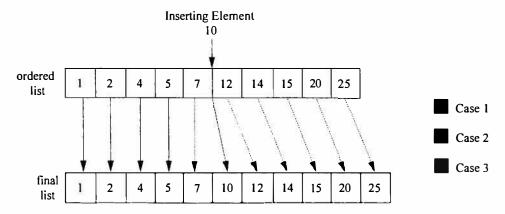

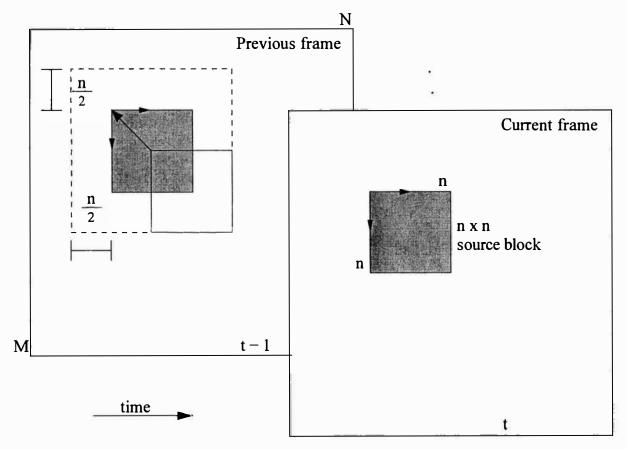

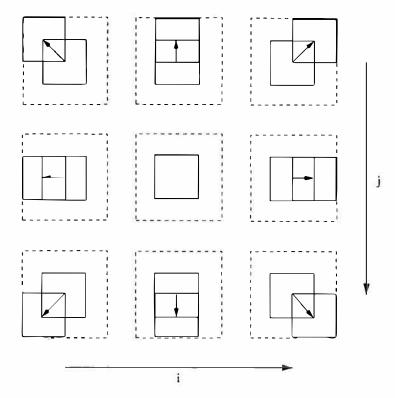

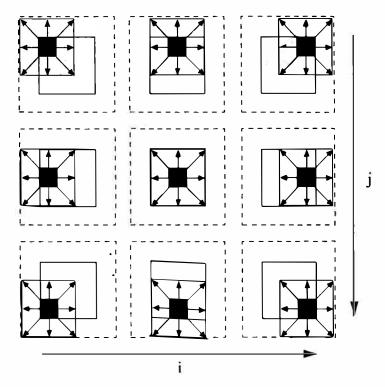

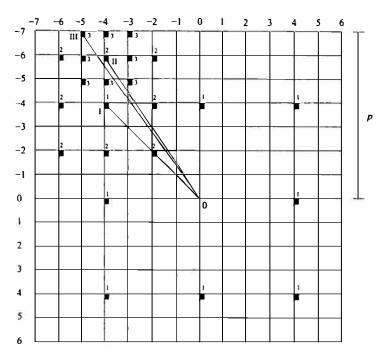

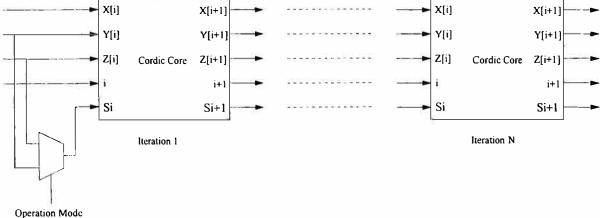

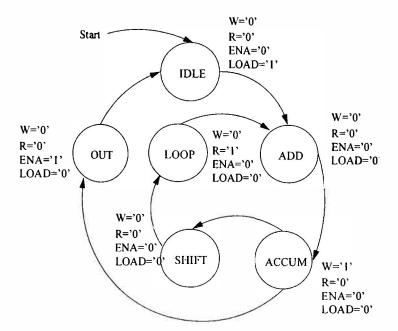

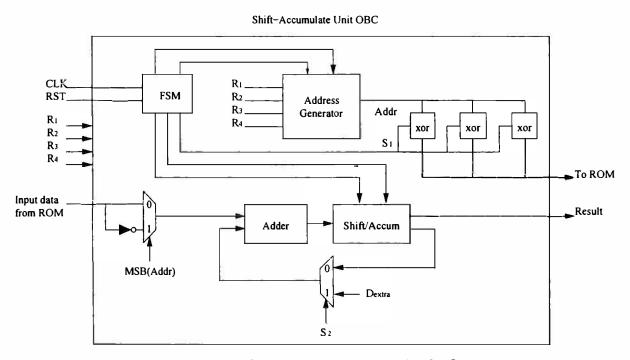

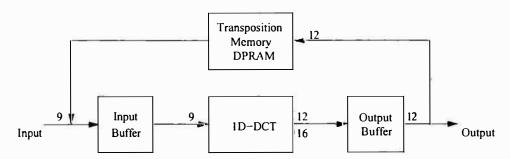

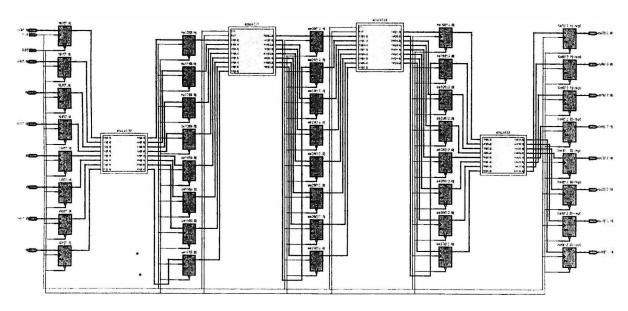

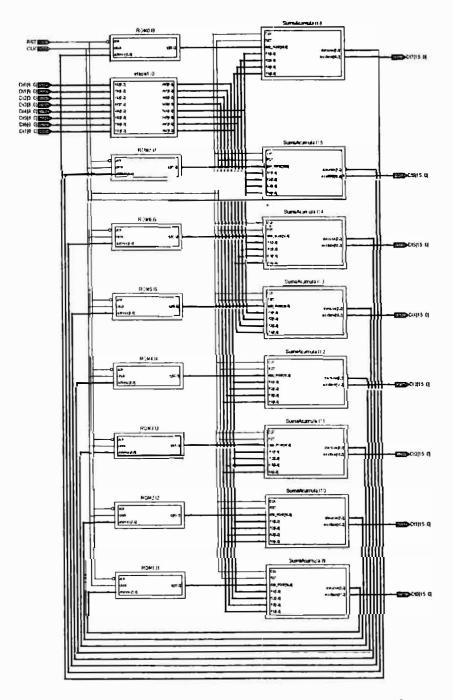

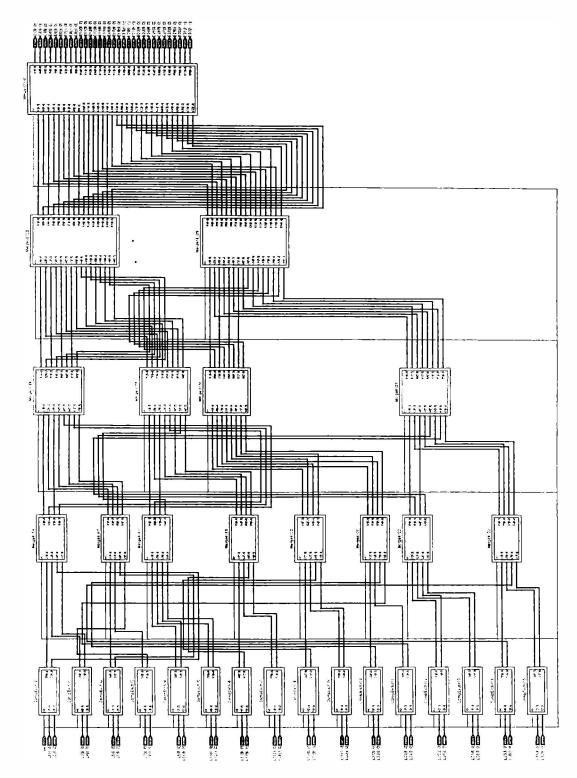

| Digital video (30 fps)                   | 60.83  Mbps            | 1.5-4 Mbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |