## INSTITUTO TECNOLOGICO Y DE ESTUDIOS SUPERIORES DE MONTERREY

## MONTERREY CAMPUS

GRADUATE PROGRAM IN MECHATRONICS AND INFORMATION TECHNOLOGIES

A VHDL-AMS Transistor Level Model of a UHF RFID Tag for System Simulation

#### THESIS

PRESENTED AS A PARTIAL FULFILLMENT OF THE REQUIREMENTS

MASTER OF SCIENCE WITH MAJOR IN ELECTRONIC ENGINEERING (ELECTRONIC SYSTEMS)

BY

Miguel Angel Rios Gastelum

MONTERREY, N. L., MEXICO, MAY, 2009

## INSTITUTO TECNOLOGICO Y DE ESTUDIOS SUPERIORES DE MONTERREY

## MONTERREY CAMPUS

## GRADUATE PROGRAM IN MECHATRONICS AND INFORMATION TECHNOLOGIES

# A VHDL-AMS Transistor Level Model of a UHF RFID Tag for System Simulation

THESIS

## PRESENTED AS A PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

## MASTER OF SCIENCE WITH MAJOR IN ELECTRONIC ENGINEERING (ELECTRONIC SYSTEMS)

BY

Miguel Angel Rios Gastelum

MONTERREY, N. L., MEXICO, MAY, 2009

## INSTITUTO TECNOLGICO Y DE ESTUDIOS SUPERIORES DE MONTERREY

#### MONTERREY CAMPUS

### GRADUATE PROGRAM IN MECHATRONICS AND INFORMATION TECHNOLOGIES

### A VHDL-AMS Transistor Level Model of a UHF RFID Tag for System Simulation

#### THESIS

# PRESENTED AS A PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

### MASTER OF SCIENCE WITH MAJOR IN ELECTRONIC ENGINEERING (ELECTRONIC SYSTEMS)

BY

Miguel Angel Rios Gastelum

MONTERREY, N.L., MEXICO. MAY, 2009

© Miguel Angel Rios Gastelum, 2009

.

## A Transistor Level Model of a UHF RFID Tag for System Simulation

BY

## Miguel Angel Rios Gastelum

#### THESIS

### PRESENTED TO THE GRADUATE PROGRAM IN MECHATRONICS AND INFORMATION TECHNOLOGIES

THIS THESIS IS A PARTIAL REQUIREMENT FOR THE DEGREE OF MASTER OF SCIENCE WITH MAJOR IN

> ELECTRONIC ENGINEERING (ELECTRONIC SYSTEMS)

## INSTITUTO TECNOLGICO Y DE ESTUDIOS SUPERIORES DE MONTERREY

MONTERREY CAMPUS

MAY, 2009

## INSTITUTO TECNOLGICO Y DE ESTUDIOS SUPERIORES DE MONTERREY

### MONTERREY CAMPUS

### GRADUATE PROGRAM IN MECHATRONICS AND INFORMATION TECHNOLOGIES

The members of the thesis committee hereby approve the thesis of Name as a partial fulfillment of the requirements for the degree of Master of Science with major in

Electronic Engineering (Electronic Systems)

Thesis Committee

Alfonso Avila, Ph.D. Thesis Advisor *Ungwo* Sergio Qmar Martínez, Ph.D.

Thesis Reader

Graciano Dieck, Ph.D.

Thesis Reader

Joaquin Acevedo, Ph.D.

Director of the Graduate Programs in Mechatronics and Information Technologies May, 2009 To my parents

.

٠

## Acknowledgements

To god, for giving me his blessing and for this opportunity to grow.

To my parents, Maria del Rosario Gastelum and Miguel Angel Rios, for your love, teachings and unconditional support.

To my brothers, Carolina and Omar Rios, for believe in me and for your support.

To my advisor, Alfonso Avila Ortega, PhD., for your teachings, guidance and friendship.

To my friends, for your patience and help.

To Consejo Nacional de Ciencia y Tecnología (CONACYT), for its sponsorship during the realization of this thesis.

And to Instituto Tecnologíco de Monterrey (ITESM), for giving me the opportunity to develop myself in this recognized institution.

#### MIGUEL ANGEL RIOS GASTELUM

Instituto Tecnolgico y de Estudios Superiores de Monterrey MAY, 2009

#### A VHDL-AMS Transistor Level Model of a UHF RFID Tag for System Simulation

Miguel Angel Rios Gastelum, M.S. Instituto Tecnolgico y de Estudios Superiores de Monterrey, 2009

Thesis Advisor: Alfonso Avila, Ph.D.

#### Abstract

The fabrication processes of Radio Frequency Identification Systems implies a large and an expensive development effort as well as very long testing periods. System modeling and cosimulation is an important approach for reduce the time to place a product into the market. This thesis presents a transistor level model of a UHF RFID tag, implemented with VHDL-AMS, for both (1)early detection of mixed signal design problems and (2)transistor level estimation of the power consumption in analog and digital subsystems. The transistor model used in the RFID tag model was implemented in VHDL-AMS and it was modeled according the characteristics of a long channel transistor. The power consumption was estimated using analog and digital components. Analog power consumption was calculated from the electric parameters of the transistor model, and digital power consumption from the switching at the output of the gates in the tag model. The functional simulation of the tag was 100% compatible with the implemented communication protocol, and the power consumption had a maximum improvement of 27.15% compared with similar research and development efforts.

# Contents

| Acknowledgements i |          |                                               |   |  |  |  |  |

|--------------------|----------|-----------------------------------------------|---|--|--|--|--|

| A                  | Abstract |                                               |   |  |  |  |  |

| 1                  | Intr     | oduction                                      | 1 |  |  |  |  |

|                    | 1.1      | Problem Description                           | 1 |  |  |  |  |

|                    | 1.2      | Objective                                     | 1 |  |  |  |  |

|                    | 1.3      | Justification                                 | 2 |  |  |  |  |

|                    | 1.4      | Contribution                                  | 2 |  |  |  |  |

|                    | 1.5      | Related Work                                  | 2 |  |  |  |  |

|                    | 1.6      | Thesis Organization                           | 3 |  |  |  |  |

| 2                  | The      | eoretical Background                          | 4 |  |  |  |  |

|                    | 2.1      | What is RFID?                                 | 4 |  |  |  |  |

|                    |          | 2.1.1 History                                 | 5 |  |  |  |  |

|                    |          | 2.1.2 Development                             | 5 |  |  |  |  |

|                    | 2.2      | Parts in a RFID System                        | 6 |  |  |  |  |

|                    |          | 2.2.1 Tag                                     | 6 |  |  |  |  |

|                    |          | 2.2.1.1 Active vs Passive Tags                | 7 |  |  |  |  |

|                    |          | 2.2.2 Reader                                  | 7 |  |  |  |  |

|                    |          | 2.2.3 Middleware                              | 8 |  |  |  |  |

|                    |          | 2.2.4 Host                                    | 8 |  |  |  |  |

|                    | 2.3      | RFID Principles                               | 8 |  |  |  |  |

|                    |          | 2.3.1 Magnetic Field                          | 8 |  |  |  |  |

|                    |          | 2.3.2 Magnetic Flux and Magnetic Flux Density | 9 |  |  |  |  |

|                    |          | 2.3.3 Inductance L                            | 9 |  |  |  |  |

|   |                | 2.3.4  | Mutual Inductance M                       | 10 |

|---|----------------|--------|-------------------------------------------|----|

|   |                | 2.3.5  | "k" Matching Coefficient                  | 10 |

|   |                | 2.3.6  | Faraday Law                               | 11 |

|   |                | 2.3.7  | The Creation of Electromagnetic Waves     | 11 |

|   |                |        | 2.3.7.1 Transition from Near to Far Field | 12 |

|   |                | 2.3.8  | Electromagnetic Waves Reflection          | 13 |

|   |                | 2.3.9  | Encrypted Data Transfer                   | 14 |

|   | 2.4            | RFID   | Applications                              | 14 |

|   | 2.4.1 Wal-Mart |        |                                           | 14 |

|   |                | 2.4.2  | E-ZPass                                   | 15 |

|   |                | 2.4.3  | SpeedPass and Contactless Payment Systems | 15 |

| 3 | UH             | F Pass | sive RFID Tag                             | 17 |

|   | 3.1            | Comm   | nunication Protocol                       | 17 |

|   |                | 3.1.1  | Power-Up Mode                             | 17 |

|   |                | 3.1.2  | Addressing Mode                           | 18 |

|   |                | 3.1.3  | Reading Mode                              | 18 |

|   | 3.2            | Trans  | ponder Arquitecture                       | 19 |

|   | 3.3            | Simula | ated Reader Signal                        | 20 |

|   | 3.4            | The R  | lectenna                                  | 22 |

|   |                | 3.4.1  | Rectifier Building Blocks                 | 22 |

|   |                |        | 3.4.1.1 Clamping Circuit                  | 23 |

|   |                |        | 3.4.1.2 Rectifier Circuit                 | 23 |

|   |                |        | 3.4.1.3 The Voltage Doubler               | 23 |

|   |                |        | 3.4.1.4 Full-wave Greinacher Rectifier    | 24 |

|   |                | 3.4.2  | Rectifier                                 | 26 |

|   |                | 3.4.3  | Power-on-Reset                            | 26 |

|   |                | 3.4.4  | Detector, Data Slicer and Decoder         | 27 |

|   |                | 3.4.5  | Shift Register and Logic                  | 29 |

|   |                | 3.4.6  | System Clock                              | 30 |

|   |                | 3.4.7  | Modulator                                 | 30 |

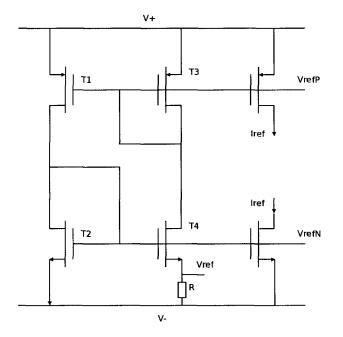

|   |                | 3.4.8  | Current Reference                         | 31 |

|   |                | 3.4.9  | Antenna Considerations                    | 31 |

-

| 4 | Tra | nsistor | Model                               | 33        |

|---|-----|---------|-------------------------------------|-----------|

|   | 4.1 | MOSE    | FET Model                           | 33        |

|   |     | 4.1.1   | Static Model of MOSFET              | 34        |

|   |     |         | 4.1.1.1 Cut-off Region              | 34        |

|   |     |         | 4.1.1.2 Linear Region               | 34        |

|   |     |         | 4.1.1.3 Saturation Region           | 34        |

|   |     | 4.1.2   | Capacitances                        | 35        |

|   |     |         | 4.1.2.1 Overlap Capacitance         | 35        |

|   |     |         | 4.1.2.2 Gate to Channel Capacitance | 36        |

|   |     |         | 4.1.2.3 Diffusion Capacitance       | 36        |

|   |     | 4.1.3   | VHDL-AMS Transistor Model           | 36        |

|   |     | 4.1.4   | Functional Tests                    | 37        |

| 5 | Ros | ults    |                                     | 41        |

| U | 5.1 |         | le's Signals                        | 41        |

|   | 0.1 | 5.1.1   | Incident RF Signal                  | 41        |

|   |     | 5.1.2   | Rectifier                           | 42        |

|   |     | 5.1.3   | Power-on-Reset                      | 46        |

|   |     | 5.1.4   | Detector                            | 48        |

|   |     | 5.1.4   | Comparator                          | -10<br>50 |

|   |     | 5.1.6   | Decoder                             | 50<br>50  |

|   |     | 5.1.7   | Current Reference                   | 50        |

|   |     | 5.1.8   | System Clock                        | 50        |

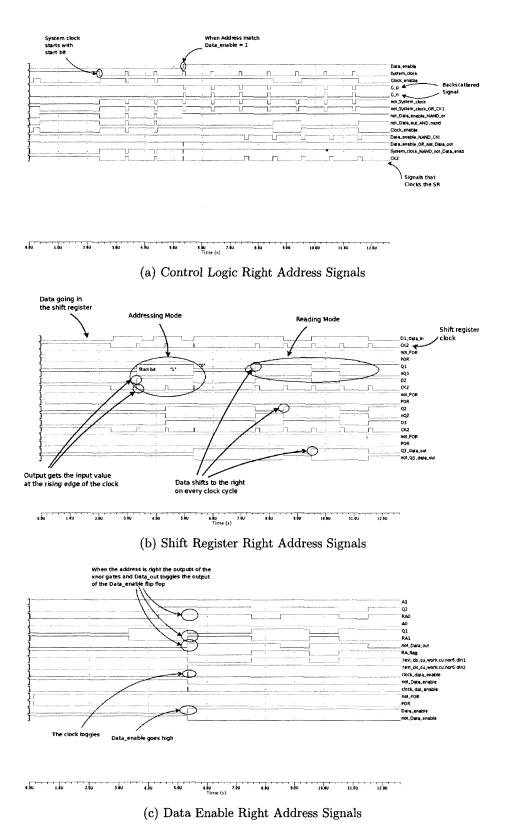

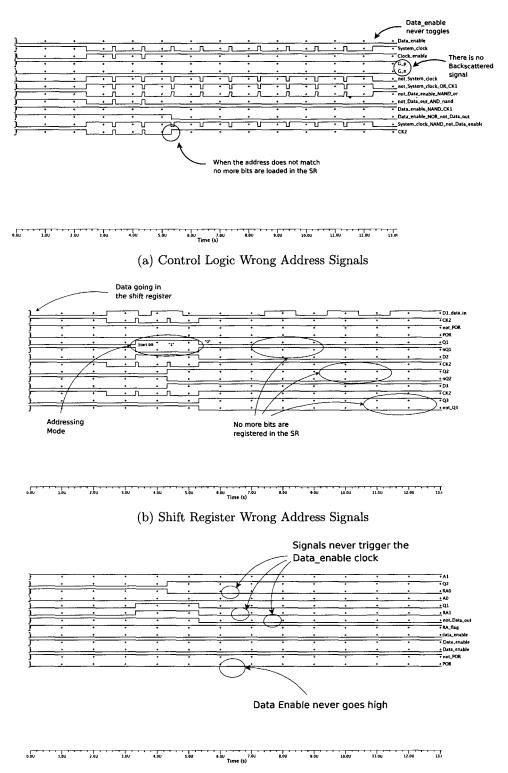

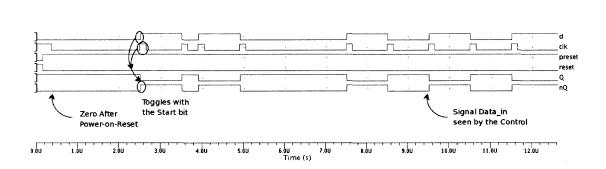

|   |     | 5.1.9   | Control Unit and Shift Register     | 50<br>52  |

|   |     | 0.1.3   | 5.1.9.1 Right Address Signals       | 52<br>52  |

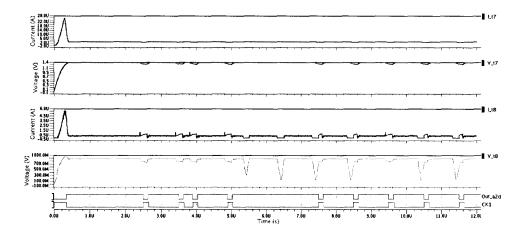

|   |     |         | 5.1.9.2 Wrong Address Signals       | 52<br>52  |

|   | 5.2 | Analo   | g Power Consumption                 | 54        |

|   | 0.2 | 5.2.1   | Incident RF Power                   | 57        |

|   |     | 5.2.2   | Rectifier                           | 57        |

|   |     | 5.2.3   | Power-on-Reset                      | 58        |

|   |     | 5.2.4   | Detector                            | 58        |

|   |     | 5.2.5   | Comparator                          | 60        |

|   |     | 5.2.6   | Current Reference                   | 60        |

|   |     | 5.2.7   | Total Analog Power Consumption      | 60        |

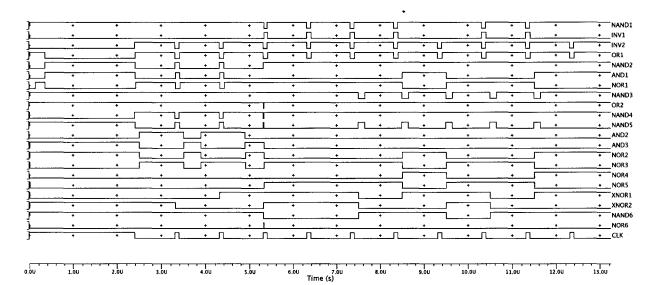

|   | 5.3  | Digital Power Consumption               | 62  |

|---|------|-----------------------------------------|-----|

|   |      | 5.3.1 Dynamic Power                     | 62  |

|   | 5.4  | Total Power Consumption                 | 65  |

|   | 5.5  | Comparison with Related Works           | 68  |

| 6 | Con  | clusions and Future Work                | 69  |

|   | 6.1  | Conclusions                             | 69  |

|   | 6.2  | Future Work                             | 69  |

| A | VH   | DL-AMS Code                             | 71  |

|   | A.1  | NMOS Transistor Code                    | 71  |

|   | A.2  | Testbench for The NMOS Transistor       | 73  |

|   | A.3  | PMOS Transistor Code                    | 78  |

|   | A.4  | Testbench for The PMOS Transistor       | 80  |

|   | A.5  | Ascending DC Source                     | 85  |

|   | A.6  | DC Source                               | 87  |

|   | A.7  | Diode Code                              | 88  |

|   | A.8  | Resistor Code                           | 89  |

|   | A.9  | Capacitor Code                          | 89  |

|   | A.10 | Flip Flop D Code and Test Bench         | 90  |

|   | A.11 | Analog to Digital Converter Code        | 93  |

|   | A.12 | System Clock Code                       | 94  |

|   | A.13 | Signal of The Reader                    | 96  |

|   | A.14 | Rectifier Code                          | 99  |

|   | A.15 | Power-on-Reser Code                     | 103 |

|   | A.16 | Detector Code                           | 105 |

|   | A.17 | Comparator Code                         | 106 |

|   | A.18 | Shift Register Logic Code               | 111 |

|   | A.19 | Current Reference Code                  | 120 |

|   | A.20 | Tag Testbench in The Wrong Address Case | 123 |

|   |      | Tag Testbench in The Right Address Case | 126 |

| в | Sigr | als of The Blocks                       | 131 |

| С | EPI  | L EKV 2.6 Transistor Code in Matlab     | 142 |

.

Bibliography

-

Vita

148

145

# List of Figures

| 2.1  | RFID System                                   |

|------|-----------------------------------------------|

| 2.2  | E-ZPass Example                               |

| 2.3  | SpeedPass Example                             |

| 3.1  | Decoder State Chart                           |

| 3.2  | Tag Operational Principles [1]                |

| 3.3  | Tag Architecture                              |

| 3.4  | Waveform of the Reader's Signal $[1]$         |

| 3.5  | Typical Rectenna Schematic                    |

| 3.6  | Diode Clamp Circuit                           |

| 3.7  | Basic Rectifier Circuit                       |

| 3.8  | Voltage Doubler Circuit                       |

| 3.9  | Full-Wave Voltage Doubler Circuit             |

| 3.10 | Full-wave Modified Greinacher Circuit [2]     |

| 3.11 | Rectifier                                     |

| 3.12 | Rectifier Equivalent Circuit [1]              |

| 3.13 | Power-on-Reset Circuit [1]                    |

| 3.14 | Detector, Data Slicer and Decoder Circuit [1] |

| 3.15 | Control Unit Circuit [1]                      |

| 3.16 | Parallel Modulator Schematic                  |

| 3.17 | Current Reference Schematic                   |

| 4.1  | MOS Capacitances                              |

| 4.2  | VHDL AMS Schematic Model    37                |

| 4.3  | $I_{DS}$ vs $V_{DS}$ NMOS                     |

| 4.4  | $I_{DS}$ vs $V_{DS}$ NMOS                     |

| 4.5  | $I_{DS}$ vs $V_{DS}$ PMOS                     |

| 4.6  | $I_{DS}$ vs $V_{GS}$ NMOS                                             | 39  |

|------|-----------------------------------------------------------------------|-----|

| 4.7  | $I_{DS}$ vs $V_{GS}$ PMOS                                             | 40  |

| 5.1  | RF Signal Received by the Transponder                                 | 42  |

| 5.2  | Rectifier Implemented in This Simulation                              | 43  |

| 5.3  | Positive Side Rectifier's Signals                                     | 44  |

| 5.4  | Negative Side Rectifier's Signals                                     | 45  |

| 5.5  | Power-on-Reset Simulation Schematic                                   | 46  |

| 5.6  | Power-on-Reset Analog Signals                                         | 47  |

| 5.7  | Power-on-Reset Digital Signals                                        | 48  |

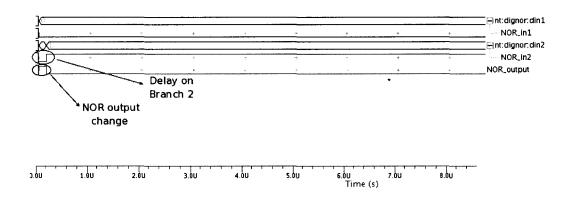

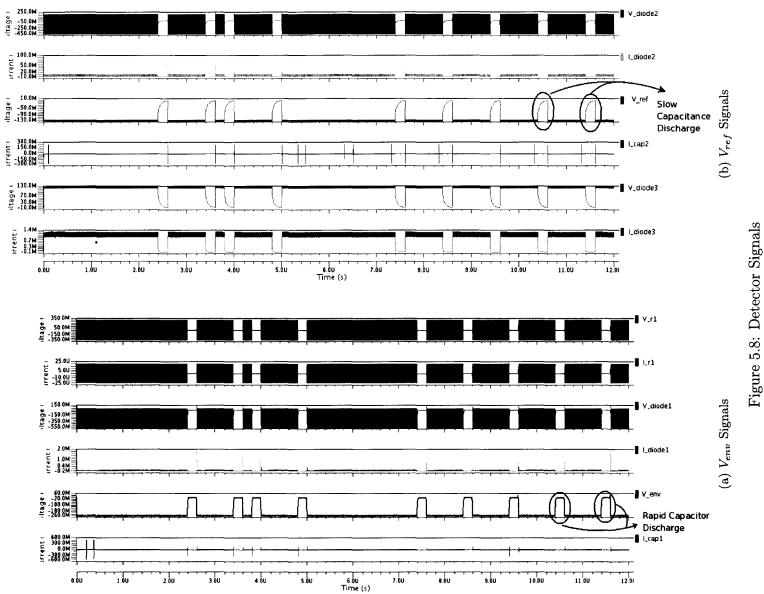

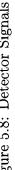

| 5.8  | Detector Signals                                                      | 49  |

| 5.9  | Comparator Signals                                                    | 51  |

| 5.10 | Decoder Signals                                                       | 52  |

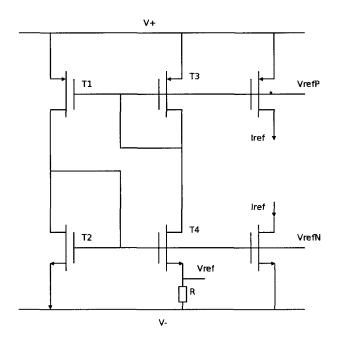

| 5.11 | Current Reference Signals                                             | 53  |

| 5.12 | Current Reference Schematic                                           | 54  |

| 5.13 | Control Unit, Shift Register and Data Enable Signals in the Right Ad- |     |

|      | dress Case                                                            | 55  |

| 5.14 | Control Unit, Shift Register and Data Enable Signals in the Wrong Ad- |     |

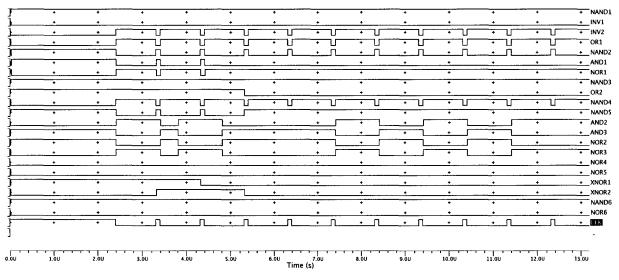

|      | dress Case                                                            | 56  |

| 5.15 | Incident RF Power                                                     | 57  |

| 5.16 | Power Dissipated By The Rectifier Block                               | 58  |

| 5.17 | Power Dissipated By The Power-on-Reset Block                          | 59  |

| 5.18 | Power Dissipated By The Detector Block                                | 59  |

| 5.19 | Power Dissipated By The Comparator Block                              | 60  |

| 5.20 | Power Dissipated By The Current Reference Block                       | 61  |

| 5.21 | Total Analog Power Dissipated                                         | 61  |

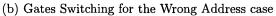

| 5.22 | Gates Switching                                                       | 64  |

| 5.23 | Right Address Case Power Consumption                                  | 66  |

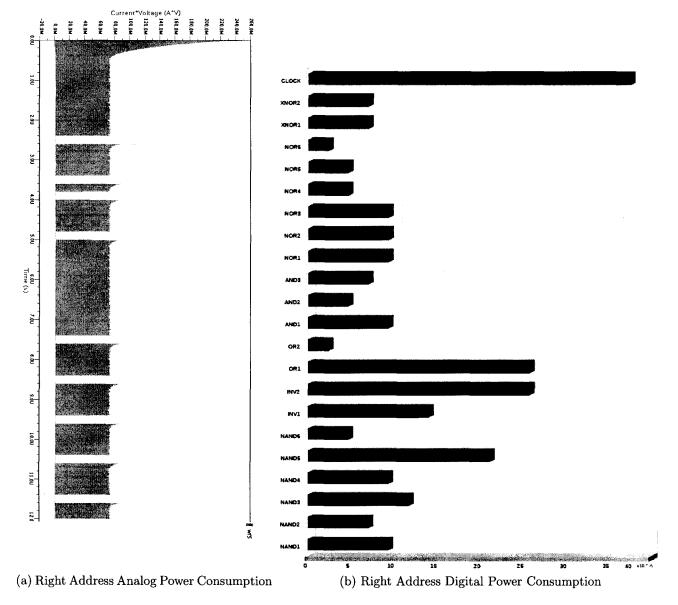

| 5.24 | Wrong Address Case Power Consumption                                  | 67  |

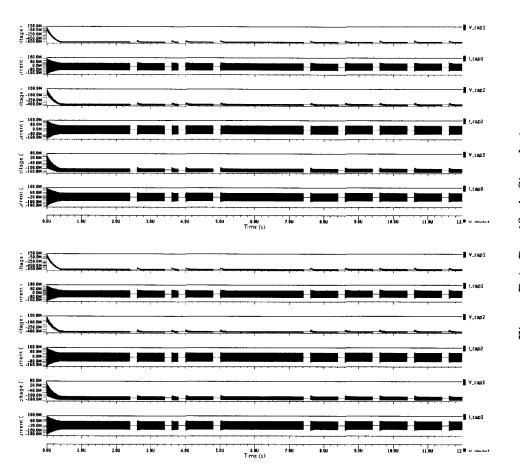

| B.1  | Rectifier's Signals 1                                                 | 131 |

| B.2  | Rectifier's Signals 2                                                 | 132 |

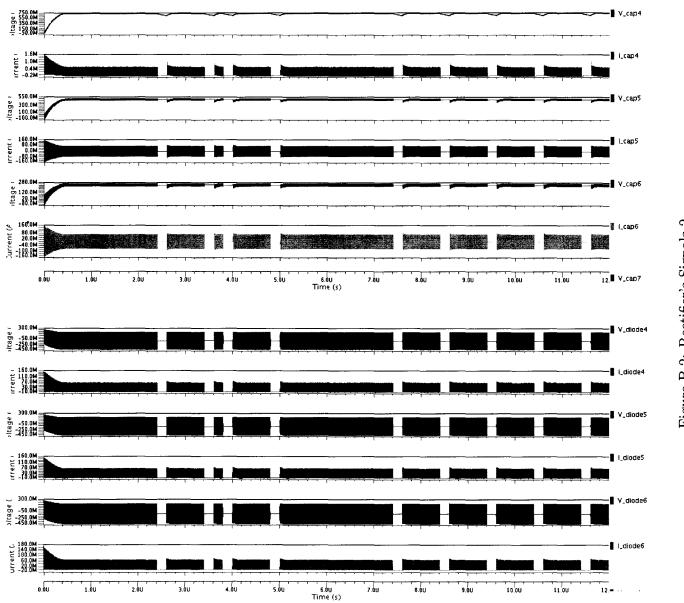

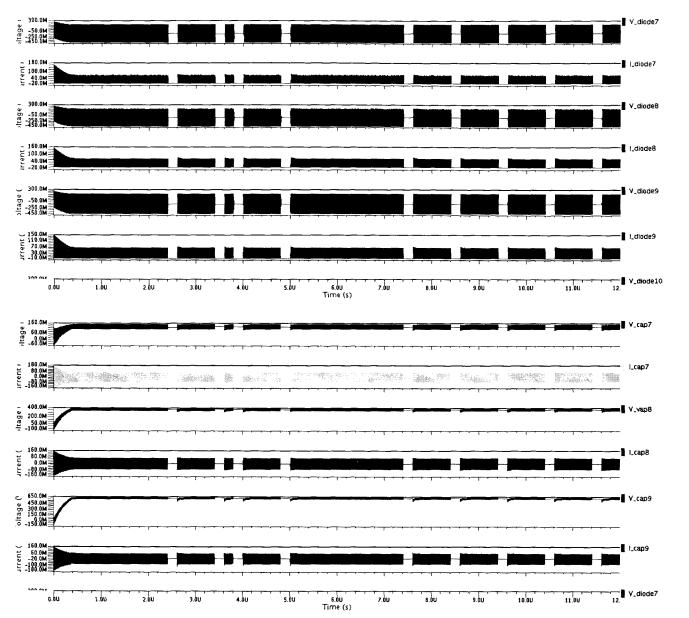

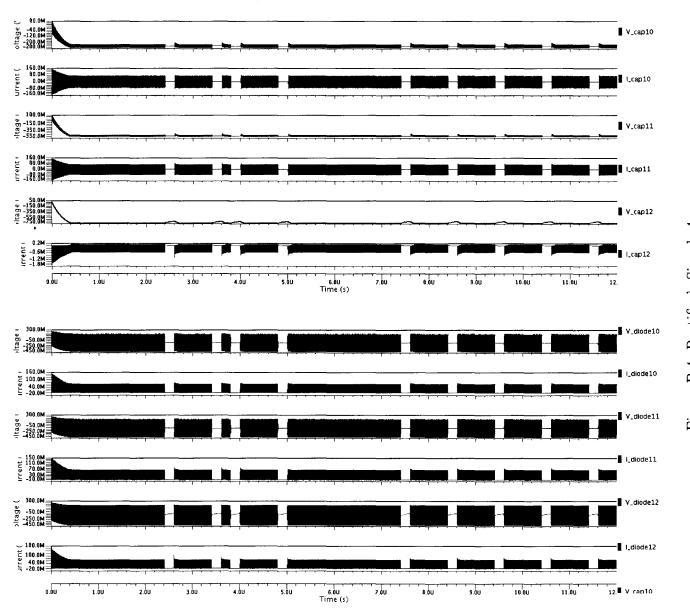

| B.3  | Rectifier's Signals 3                                                 | 133 |

| B.4  | Rectifier's Signals 4                                                 | 134 |

| B.5  | Power-on-Reset's Signals                                              | 135 |

| B.6  | Detector's Signals                          | 136 |

|------|---------------------------------------------|-----|

| B.7  | Comparator's Signals                        | 137 |

| B.8  | Decoder's Signals                           | 138 |

| B.9  | Current Reference's Signals                 | 139 |

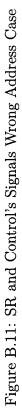

| B.10 | SR and Control's Signals Right Address Case | 140 |

| B.11 | SR and Control's Signals Wrong Address Case | 141 |

-

# List of Tables

| 3.1 | Characteristics of the Reader's Signal                            | 21 |

|-----|-------------------------------------------------------------------|----|

| 3.2 | Characteristics of the System Clock                               | 30 |

| 4.1 | Channel Capacitance in the Different Regions of Operation         | 36 |

| 5.1 | Percentage of Total Power Consumption                             | 62 |

| 5.2 | Switching Factor and Power Consumed by Each Gate In The Right Ad- |    |

|     | dress Case                                                        | 63 |

| 5.3 | Switching Factor and Power Consumed by Each Gate In The Wrong     |    |

|     | Address Case                                                      | 65 |

| 5.4 | Dynamic Power Consumption Comparison                              | 65 |

| 5.5 | Comparison of Results with Works [3] and [4]                      | 68 |

| 5.6 | Comparison of Results with [5]                                    | 68 |

# Chapter 1

## Introduction

## **1.1** Problem Description

The development and testing of RFID systems requires some time to integrate digital and analog components. Once the RFID system is fabricated and ready for testing, the detection of design errors slows down the time needed to deliver the system to the market resulting in monetary losses. The development time for RFID systems could be shrunk with adequate system models that allow the designers to have better system simulation methodologies for faster error detection. Most of the models of RFID components describe the behavior at the functional level. These models lack of the required granularity to provide accurate estimations of power consumption.

## 1.2 Objective

The main purpose of this research is to reduce the development times of RFID systems and detect errors in early stages of the design. The creation of a transistor level model of an RFID tag in VHDL-AMS is proposed to accomplish those goals. The idea is to obtain power consumption estimations from the transistor level model. A modular architecture with mixed signals interconnections between different blocks is intended. The proposed RFID architecture could add extra components in future research projects.

## **1.3 Justification**

Today, the design of Radio Frequency Identification (RFID) systems needs a short development time, to reach the market as soon as possible without absorbing extra costs of NRE (non-recurring engineering) hours. The fast time to market can be achieved with system models design and cosimulations. System models allow the cosimulation between analog and digital parts of the system before assuming the high costs of fabrication of the chip. Cosimulation shows the behavior of the System and important information can be obtained from it, like power consumption and the behavior of the systems sigals.

## 1.4 Contribution

The contributions of this thesis are:

- 1. A MOSFET transistor model using VHDL-AMS

- 2. The modeling and cosimulation of a complete mixed signal RFID tag using VHDL-AMS

- 3. Accurate measurements of power consumption at transistor level for the analog and digital components

### 1.5 Related Work

An RFID antena model in VHDL-AMS was developed and cosimulated. This effort focuses on studying the power absortion at the RF link [27]. References [3] and [4], show the implementation of a low power active RFID using both, an FPGA and a SoC. They also measure the power consumption directly from the physical components. A new contactless smartcard with an integrated 8-bit microcontroller is described in [6]. The smartcard was implemented in a SoC and demonstrates that the integrated power reception and management, Radio Frequency communication and signal processing are possible in SoC with its characteristics. Reference [7] presents an RFID system with a fully integrated transponder fabricated in standard CMOS 0.18 process. It uses a near field coupling for enable the on chip tag's antenna. An architecture for a RFID tag that includes a microprocessor is presented in [8]. Some novel low power technologies for low power microprocessor are adopted, the power consumed by the subsystems is analized in the chip implementation of the tag. A novel simulation concept for functional verification based in cosimulation is presented in [5], it combines system level models of the RFID system with hardware level description of components, and with this defines the energy consumption of the tag. This thesis estimates the power consumption of an RFID tag before fabrication using the cosimulation methodology. The near field coupling is considered in the cosimulation for the tag power up and no physical implementation is needed to verify the bahavior of the tag.

## 1.6 Thesis Organization

Chapter 1 presents the problem description, objective, justification, contribution and related work of this Thesis. Chapter 2 presents the necessary Theoretical Background in RFID systems. Chapter 3 covers the Tag's Architecture used in the simulations of this research work. Chapter 4 presents the transistor model implemented in the Architecture. Chapter 5 shows the results obtained from the simulations, and finally Chapter 6 presents conclusions and future research possibilities.

# Chapter 2

## **Theoretical Background**

## 2.1 What is RFID?

All radio transmissions that contain any kind of identification information are considered as Radio Frequency Identification (RFID). RFID involves devices that can exchange data using radio signals. The usual system involves a small tag that identifies a specific object. The specific object is identified by sending a radio signal to the tag, this one interprets it and returns the identification information stored. Sometimes this process can be as complex as using cryptographically encoded data, sending it via satellite and store it in a database[9].

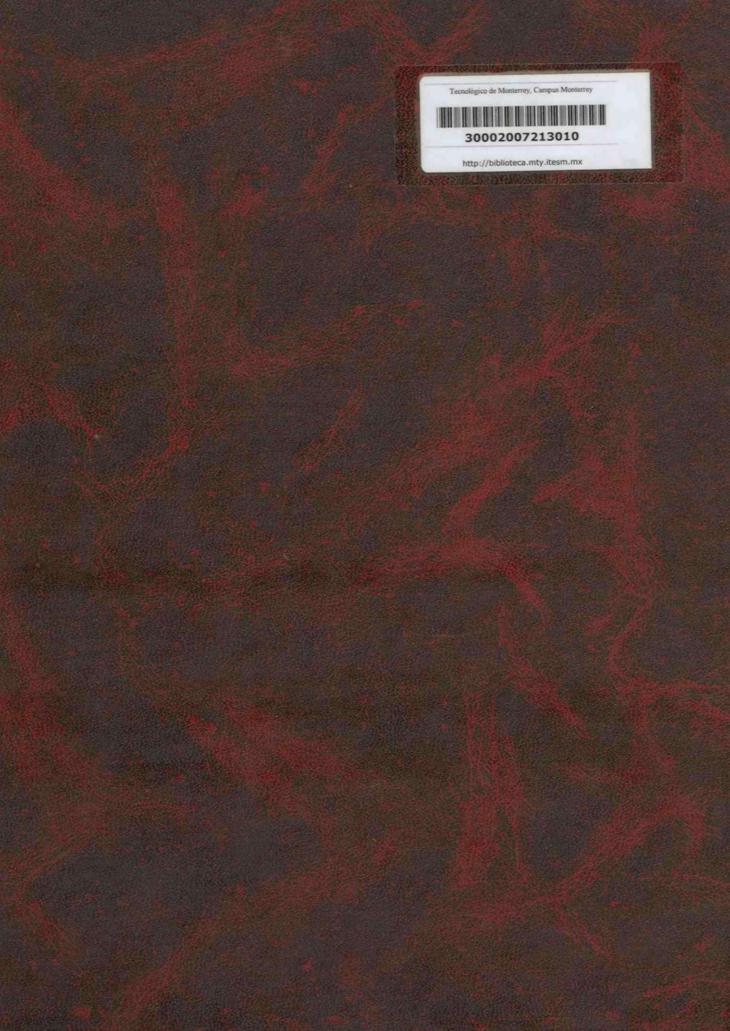

Figure 2.1: RFID System

#### 2.1.1 History

In the year of 1906 Ernst F. Alexanderson demonstrate with his work the first continuous wave radio generation of radio signals, this marked the beginning of the modern radio communications. Also the early 20nth century was considered the birth of the RADAR and it developed extensively in the World War II. RFID was conceived as a combination of the previous technologies. One of the first works talking about RFID was the landmark paper "Communications by Means of Reflected Power", by Harry Stockman, published in 1948. This work talked about the research needed to develop the reflected power communications and that a lot of research was needed before this technology was widespread. In fact, 30 years had to pass before the vision of this man was possible, the development of the transistor, the integrated circuit, the microprocessor, communication networks had to be done before. The 1930's and 1940's was the era when the radar had much technical developments and this brought exploring RFID techniques. One of the first explored applications was the "long range transponders systems" for identification of enemy or foe air crafts in the World War II[10].

#### 2.1.2 Development

The 1960's developments created the bases for the 1970's RFID explosion. In 1964 R.F. Harrington studied the electromagnetic principles related to the RFID technology and published his work in a paper named "Theory of Loaded Scatterers". This decade was also the beginning of RFID in the commercial activities with companies like sensormatics being founded and applications like "Electronic Article Surveillance" being developed[11].

The 1970's was a decade of RFID intensive research, everyone was working on it, getting important advances. The use of passive RFID tags was achieved in the work named "Short-Range Radio Telemetry for Electronic Identification Using Modulated Backscatter" developed by Los Alamos Cientific Laboratory. In that work they talked about completely passive tags with operational ranges of about tens of meters. Large companies like Raytheon's Raytag and RCA were also involved in the development of RFID technology. RFID as a lot of other electronic technologies got benefits from the development of the low-power CMOS logic circuits since this permitted RFID systems to use smaller tags with less power consumption which was ideal because they were intended to be passive. The 1980's was an implementation era, there was a lot of interest in develop applications for the close range detection of animals, toll roads and industry automatization. The arrival of the personal computer (PC) was an important aid to manage RFID data, so it could be implemented everywhere a PC was present. By this time tags were built with CMOS technology and the EEPROM became the memory of choice, this lead to important size reductions in the tag and increase the functionality.

The 1990's was an important time for RFID, electronic toll collection was implemented all around the United States, it allowed vehicles to access different areas, like parking lots, highways and stadiums, using a single tag in each vehicle. The first highway with these characteristics was founded in Oklahoma, and then states like Texas and Georgia followed. A single protocol for all these highways was created. A notable application was the one developed by Texas Instruments, named TIRIS, which allowed an automobile user to control the start of the engine[12]. More countries join the use of RFID technologies, like Australia, China, Mexico and Canada. A great number of companies entered the marketplace because of the growing interest on items management and the opportunity of work along bar codes.

In the 21st century the main preoccupations of RFID is to create a standard to unify all the areas of these technologies. At this point two organizations are taking the lead, EPCGlobal and ISO. A lot of interest is also focused in the development of telematics, article tracking, supply chain management and mobile commerce.

The future looks great for RFID but it still needs improvements in other areas as software development, privacy policies and infrastructure in RFID systems. But nothing great was achieved without enthusiasm, so there a lot of that need to be developed before RFID get the best it can [10].

## 2.2 Parts in a RFID System

#### 2.2.1 Tag

RFID units are in the radio devices class also known as transponders. A transponder is a combination of a transmitter and a receiver It receives a specific radio signal and returns a reply. In the simplest implementations, the transponder just listen to a specific radio signal and its reply consists in just backscattered radio signal. In more complex cases the reply can consists of a string of letters or numbers. Transponders used in RFID systems are commonly called "tags", "chips" or "labels". As a general rule, a RFID tag contains the following items:

- Encoding/Decoding Unit

- Memory

- Antenna

- Power Supply

- Communication Control

Depending on the type of tag and the application, the amount of information carried can change, from a few bytes to a few megabytes[13].

#### 2.2.1.1 Active vs Passive Tags

Tags fall into two categories: "active" and "passive". Passive RFID tags do not contain a power supply, they get their energy from the electromagnetic signal provided from the reader. To obtain the power from the reader they need to use an electromagnetic property known as "Near Field". Because this property the transponder can obtain enough power to send a response. Active RFID tags have their own power supply. Since they have power all the time, they can transmit and receive on their own without having to be in the near field. They can reach larger distances due to their power independence [14].

#### 2.2.2 Reader

The second more important component is the reader, that is also a transceiver. His role is to interrogate a tag and receive data from it. It can contain an antenna as an integral or separated part of it, it can also have other elements like: RS-232 serial port, Ethernet jack, cryptographic encoding or decoding, a power supply battery or a communication control circuits. The reader retrieves the information contained in the RFID tag, and can store it locally or send it to a database.

#### 2.2.3 Middleware

The middleware manages the reader and the data received from the tag and has the purpose of store the data in a database. The middleware is in the middle of the communication between the database and readers and it can perform another functions as filter the information.

#### 2.2.4 Host

The host can also be known as the database and it can be a standard commercial database such as SQL, MySQL, Oracle, etc. Depending on the application the host can be a PC or multiple mainframes networked together via global communication systems[14].

## 2.3 **RFID** Principles

The major part of the RFID systems operates under the inductive coupling principle, therefore it is necessary to understand the magnetic phenomenon to have a clearer idea on how power and data are transmitted from the reader to the tag in a RFID system.

#### 2.3.1 Magnetic Field

Every moving charge in a conductor is associated to a magnetic field. The intensity of the magnetic field can be described by the equation of magnetic field strength "H". In a general form it can be say that the sum of the currents in a closed curve is equal to the contour integral of the magnetic field within it.

$$\sum I = \oint \vec{H} \cdot \vec{ds} \tag{2.1}$$

Equation 2.1 can be used to calculates the magnetic field strength. In a straight conductor the field strength "H" along a circular flux line at a distance "r" is constant.

$$H = \frac{1}{2 \cdot \pi \cdot r} \tag{2.2}$$

The path field of strength "H(x)" in conductor loops or "short cylindrical coils" are used to generate the magnetic alternating field in the write/read devices of RFID systems working under the inductive coupling principle. An in depth analysis shows that when you move the measurement point away from the center of the coil the field strength decrements in proportion with the distance. Equation 2.3 calculates the path field strength along the "x" axis or around the coil:

$$H = \frac{I \cdot N \cdot R}{2 \cdot \sqrt{(R^2 + x^2)^3}}$$

(2.3)

where "N" is the number of winding of the coil, "R" is the circle radius "r", "x" is the distance from the center of the coil in the "x" direction. The following boundaries have to be applied:  $d \ll R$  and  $x < \frac{\lambda}{2\Phi}$ .

#### 2.3.2 Magnetic Flux and Magnetic Flux Density

If a soft iron core is introduced in the center of a coil, leaving everything else equal, the magnetic field strength will keep constant but the flux density, the total number of flux lines, will increase, and this is fundamental for the force generation. The magnetic flux  $\phi$  is the total number of lines of magnetic flux that passes through the inside of a cylindrical coil. Magnetic flux density "B" is a variable related to the area "A". Magnetic flux is expressed as:

$$\Phi = \int \int_{s} \vec{B} \cdot \vec{ds} \tag{2.4}$$

In the special case where the surface "S" is a planar surface with area "A", and the magnetic field is constant with magnitude "B", the formula simplifies to:

$$\Phi = B \cdot A \cdot \cos \theta \tag{2.5}$$

where  $\theta$  is the angle between "B" and the surface normal to "S".

The relationship between the density flux and field strength is given by:

$$B = \mu \cdot H \tag{2.6}$$

Where  $\mu$  is a material dependent parameter called the permeability.

#### 2.3.3 Inductance L

A magnetic field and a magnetic flux are both generated around a conductor of any shape but it will particularly intense in a loop form conductor. There are conductor spirals and each of them contributes on the same proportion to the total flux, thus:

$$\psi = \sum_{N} \Phi_N = N \cdot \Phi \tag{2.7}$$

The ratio of the flux that arises in an area enclosed by a current, to the current in the conductor that encloses it is named inductance L. By definition its formula is:

$$L = \frac{\psi}{I} = \frac{N \cdot \Phi}{I} \tag{2.8}$$

Inductance is one of the variables of conductor loops or coils. It depends of the material properties, the space that the flux flows through and the geometry of the conductor.

#### 2.3.4 Mutual Inductance M

If a second conductor loop is placed near of the first conductor loop and for which a current is flowing, then this will be subject to a proportional of the total magnetic flux flowing through the firs conductor loop. The two circuits are coupled by this partial flux. The magnitude of this coupling flux depends on the geometric dimension of both conductor loops, their positions relative to each other and the magnetic properties of the medium. The definition of self inductance is the ratio of the partial flux from the second conductor loop to the first one to the current in the first conductor loop.

$$M_{21} = \frac{\psi_{21} \cdot (I_1)}{I_1} = \oint_{A2} \frac{B2 \cdot (I_1)}{I_1} \cdot d \cdot A_2$$

(2.9)

Similarly is a mutual inductance in the inverse way and the next relationship applies:

$$M = M_{12} = M_{21} \tag{2.10}$$

Mutual inductance describes the coupling of two circuits through a magnetic field. Inductively coupled RFID systems are based on this principle.

## 2.3.5 "k" Matching Coefficient

We talk about a coupling between two conductor loops that are near one another, now the matching coefficient can tells how big is this coupling, and depending on their geometric the following applies:

$$k = \frac{M}{\sqrt{L_1 \cdot L_2}} \tag{2.11}$$

This coefficient always varies between  $0 \le k \le 1$ .

- k = 0 for full decoupling

- k = 1 for total coupling, both conductor loops are subject to the same magnetic flux

In practice, coupled conductor loops can operate with "k" coefficients that may be as low as 0.01.

#### 2.3.6 Faraday Law

A change in the magnetic flux  $\Phi$  generates an electric field strength " $E_i$ ". This is described by "Faraday's law". The effect of the magnetic field depends on the material surrounding it. A special interest is given to the effect caused in a metal surface. An electric field is induced in the metal surface that causes free charge carriers to flow in the direction of the electric field. Currents flowing in circles are created and are named "Eddy currents", they work against the magnetic flux, which may damps it significantly near metal surfaces. The "Eddy currents" are undesirable in inductively coupled RFID systems, so they are reduced by using ferrite shielding in metallic environments. In its general form, the Faraday's law can be expressed as:

$$u_i = \oint \vec{E_i} \cdot \vec{ds} = -\frac{d\Psi(t)}{dt} \tag{2.12}$$

For a configuration of N windings, Faraday's law can also be expressed as  $u_i = N \cdot \frac{d\Psi}{dt}$ . As a RFID example of the Faraday's law, lets suppose that we have two conductors loops in a near distance between them and a time variant current is applied through one of them. This current will generates a time variant magnetic flux and a voltage in both conductor loops. In RFID systems, one conductor loops would be the reader antenna whiles the other the transponder antenna. The reader antenna induces a voltage and also a current in the transponder side due to the resistance of the conductor and the resistance of the memory, this current also generates a magnetic field that opposes the magnetic flux generated by the readers antenna[15].

#### 2.3.7 The Creation of Electromagnetic Waves

A varying magnetic field in space induces an electric field with closed field lines. The electric field varies in time and surrounds the magnetic field. Due the variation of the electrical field a magnetic field in space is generated and it also surrounds the electric field and varies over time. Because of the mutual dependence of the time varying fields there is a number of effects on the magnetic and electric fields.

Radiation can only occur when a finite propagation speed is given for the electromagnetic field, which prevents a change in the voltage of the antenna from being followed immediately by the field in the vicinity of the charge. Because this radiation limitation, even the alternating voltage's zero crossover, the field lines from the previous half wave remaining in space cannot end at the antenna, but close into themselves forming eddies. Eddie currents are formed in the opposite direction of the ones formed in the next half wave propelling them and thus propelling the energy stored in the field away from the emitter at the speed of light. The electromagnetic field is interlinked with the electrical field that propagates at the same time. When a certain distance is reached, the fields are released from the emitter, this point represents the beginning of the electromagnetic radiation. At high frequencies, the radiation is more effective because the magnetic radiation takes place near the emitter, where the strength of the field is high, that means small wavelengths. The wavelengths can be calculated as:

$$\lambda = \frac{c}{f} \tag{2.13}$$

In the far field exists a relationship between the electric and the magnetic field, both fields are linked by the field characteristic impedance:

$$Z_F = \frac{E}{F} = \sqrt{\mu_0 \varepsilon_0} = 376.73\Omega \tag{2.14}$$

Electromagnetic waves propagates quasi-optically in the far field (free space). The field strength falls as the distance from the emitter increase. Equation 2.14 describes the free space attenuation from a source to a point at a distance d:

$$a_f/dB = -147.6 + 20\log(d) + 20\log(f)$$

(2.15)

#### 2.3.7.1 Transition from Near to Far Field

The primary magnetic field begins at the antenna and induces electric field lines in space. This area is known as near field. At the distance of  $\lambda/2\pi$  the electromagnetic field separates from the antenna and wanders into space as an electromagnetic field. This separated electromagnetic field is named far field. A separated electromagnetic wave have no direct effect in the antenna from which it was generated. For inductively

coupled RFID systems this means that when the far field begins, a transformer-type coupling is no longer possible. The radius  $r_f = \lambda/2\pi$  around the antenna represents an insurmountable range limit for inductively coupled systems [16].

#### 2.3.8 Electromagnetic Waves Reflection

An electromagnetic wave emitted by an antenna can encounter various objects. Part of the energy that reaches the object is absorbed by it, the other part is scattered in many directions with different intensities. A small part of the scattered energy finds its way back to the emitter. RADAR technology uses this reflection to measure the distance and position of distant objects. In RFID systems, the reflection of electromagnetic waves is used for the transmission of data from the transponder to the reader. Reflective properties of objects generally increase with higher frequencies. RFID systems are used in frequencies ranges from 915 MHz to 2.45 MHz or higher. Let's consider this specific case, the high frequency generated by the reader is emitted in all directions, so the power density "S" at the transponder is:

$$S = \frac{P \cdot G}{4\pi \cdot R^2} \tag{2.16}$$

where "P" is the transmission power from the reader, "G" is the antenna gain of the transmitter and "R" is the distance between reader and antenna. The power reflected for the transponder is proportional to the power density:

$$P_2 = \sigma \cdot S \tag{2.17}$$

The radar cross section  $\sigma$  is the measure of an object ability to reflect electromagnetic waves. It depends of a range of parameters as object size, shape, material, surface structure but also wavelength and polarization. Equation 2.17 describes the power density that returns to the reader:

$$S_{back} = \frac{P \cdot G\sigma}{(4\pi)^2 \cdot R^4} \tag{2.18}$$

The reception power of the receiver antenna can be determined from its effective absorption area  $A_w = \lambda^2 x G/4\pi$ :

$$P_{back} = \frac{P \cdot G \cdot \sigma \cdot A_w}{(4\pi)^2 \cdot R^4} = \frac{P \cdot G^2 \cdot \lambda^2 \cdot \sigma}{(4\pi)^3 \cdot R^4}$$

(2.19)

From the previous section it can be concluded that the reading range of a backscattered RFID system is proportional to the fourth root of the transmission power of the reader[17].

#### 2.3.9 Encrypted Data Transfer

In RFID, data transmission can suffers two types of attacks: an attacker can behave passively and tries to eavesdrop into the transmission to get confidential information and use it on his benefit. In the other kind of attack, and intruder behaves actively to manipulate the transmission data and alter them to his own benefit. Cryptological procedures are used to protect the data transmission from both active and passive attackers. Modifying the data before the transmission takes place can confuses an intruder to avoid him from getting conclusions. Encrypted data transmissions always follows the same order, first the data to be sent is transformed into a cipher data using a secret key and a secret algorithm. Because the attacker does not know the secret algorithm nor the secret key, he cannot interpret the data and it is not possible to recreate the transmission data from the cipher data. The information is transformed back to its original form in the receiver using the secret algorithm and secret key. RFID systems use the same key to ciphering and deciphering so it is a symmetrical key procedure[15].

## 2.4 **RFID** Applications

#### 2.4.1 Wal-Mart

In June 2003 the Wal-Mart CIO and vice president Linda Dillman made an announcement, later called a mandate, requiring Wal-Mart's top 100 suppliers to use RFID on cases and pallets of inventory shipped to the retailer by January 1, 2005. Wal-Mart have 9% of retail sales in the world so this was a big new for the RFID growth. This mandate tells the suppliers to use passive RFID tags in all the shipments sent to three of Wal-Mart's distribution center in Texas. Once the deadline was met and the pallets with RFID starts to arrive, Wal-Mart reported more than five million tag reads. The results on this mandate were:

- A 16% reduction in out-of-stock items because of the use of EPC tags

- Out-of-stock items are replenished three times faster using EPC instead bar codes

- RFID-equipped stores were 63% more effective at replenishing out-of-stock items

A research firm named Sanford C. Bernstein & Co. estimated that Wal-Mart could save over \$8 billion annually once RFID is fully deployed in all of its locations[18].

#### 2.4.2 E-ZPass

E-ZPass is a RFID-enabled payment system for the highways installed in about 25 states in the United States. It was conceived with the idea of prevent traffic congestion and delays in the roads. E-ZPass Interagency Group was created in 1991. In order to use this payment systems, drivers have to create a prepaid account with a check or a credit card and get in return an active RFID transponder that works at a frequency of 900MHz. Readers are placed in the traffic lanes. As the car passes through the designated E-ZPass lane in the toll place, the system detects the cars with the E-ZPass transponder associating them to their account and charging the toll cost. Despite the complains of the public because of the facility of the government to look at the information of the cars that use E-ZPass, this is one of the more successful deployments of RFID in a consumer facing setting, with more that ten years of commercial use[14].

Figure 2.2: E-ZPass Example

#### 2.4.3 SpeedPass and Contactless Payment Systems

This system consists on a card that can achieve electronic payment without having to slice the card, all what it needs is to be near a reader, usually a few inches, and the payment is done automatically. Exxon, MasterCard and Chase bank have some of this payment systems. Other variant of this contactless systems is the Near Field Communication. With this method a mobile phone can be waved in front of a reader and the payment is completed. Contactless payment systems were introduced in 1997. All contactless payment systems contain passive RFID tags in different devices as credit cards, mobile phones or keys. These devices contain a cryptographically enabled RFID chip and an antenna, the points of sale have a reader installed. When is time to pay, the reader interrogates the tag and check the credit in the database, if the credit is approved the purchase is finished, charging the amount of money to the costumers account. Speedpass is one of the most successful RFID deployments because of the large number of people using it, despite some security problems related to the immunity of the credit card at the time of the transaction[19].

Figure 2.3: SpeedPass Example

# Chapter 3

# UHF Passive RFID Tag

This simulation is based on an ultra-low power consumption transponder model developed in [1], with some differences. This chapter shows the bases of the communication protocol used to establish the link between the reader and the transponder, the architecture of the transponder and the way each functional block works.

# **3.1** Communication Protocol

A special protocol is used in this application. iIt does not implement the available standards, like ISO 18000-6 or EPCGlobal, although it can be easily modified to be compliant with them. Every step of the protocol is controlled by the reader due to the limited intelligence that can be embedded in the tag. The sessions are split into three parts: power-up mode, addressing mode and reading mode.

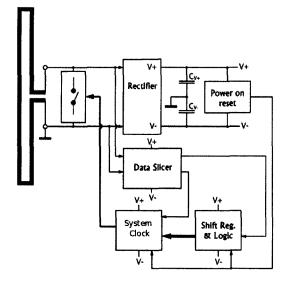

#### 3.1.1 Power-Up Mode

A reader emits the RF power to a certain area where one or more transponder are located. Any transponder, receiving the RF power, absorbs it using its antenna and converts it to DC using the rectifier. The DC current energizes the tag's subsystems. During this mode, a power-on-reset signal is generated, turning on all the circuitry in the transponders and putting them into the addressing mode.

#### 3.1.2 Addressing Mode

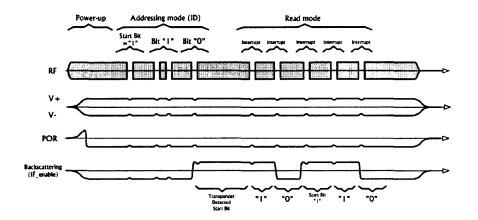

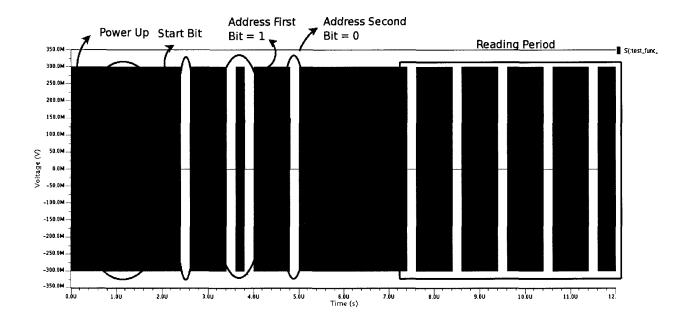

In this mode, all the energized transponders wait for the reader to send data. The reader sends a string of data with a serial number in it to all the transponders. All the transponders receive the serial number and compare it with its own serial number. If the serial number matches the ID of one transponder, the transponder goes to the reading mode, as the others change to quiet mode. The requested transponder now modulates its input impedance to backscatter the reader's signal so it can detect its presence. The transponders in quiet mode wait for a power off or probably a new interrogation session. Under this protocol no collision problem are possible as only one transponder can hold a communication sesion with the reader at once. To send an address, the reader generates a series of 200ns interrupts in the RF signal. The duration of the interrupts should be short to avoid the transponder going off and triggering a new power-on-reset. The start bit is always a logical "1" and corresponds to only one RF interrupt. For the following bits, the reader sends two RF interrupts if the next bit has the same logical value than the preceding one and only one interrupt otherwise, as shown in Figure 3.1. The gap between two successive interrupts is about 200 ns. The time between two successive bits has to be greater than twice gap size. This protocol implementation is very simple and offers low power consumption.

#### 3.1.3 Reading Mode

Only the transponder matches the requested ID jumps into this mode. The shift register is locked by the control logic. The clock turns on and off the modulator to backscatter the signal from the reader and acknowledgs its presence. The reader realizes that an active transponder is in the interrogation area and sends short RF interrupts similar to the star bit. The tag receives and decodes the interrupts that work as a clock signal for the shift register whose output is the next bit of information. When the next bit is a logical "1" the transponder keeps the clock on and backscatters the readers signal. If the next bit is a logical "0", the clock is turned off and no backscattered signal exist, so the reader takes it as a "0". The way the decoder work is shown in Figure 3.1.

For each one of the interrupts sent by the reader in the reading mode, the transponder cycles the shift register and the reader can confirms that the serial number sent matches the received one. In this work, the returned data from the transponder to the reader is the transponder's ID, but, it can be modified to send other kind of informa-

Figure 3.1: Decoder State Chart

tion. The signals shown in Figure 3.2 are a comprehensive example of a session for a three bits transponder, the same used in this work.

Figure 3.2: Tag Operational Principles [1]

# **3.2** Transponder Arquitecture

Figure 3.3 shows all the functional blocks of the transponder simulated in the present work. Passive transponders, as discussed in section 2.2.1.1, get their energy by rectifying the RF input in their antenna. This energy is, then, stored in capacitors to obtain a DC power supply. A power-on-reset signal is generated, with enough energy at the transponder, to wake up the transponder subsystems. Next, the transponder listens to the data sent by the reader and decodes it. This architecture is simple compared to other communication systems. The only RF parts are the modulator, the envelope detector and the rectifier.

Figure 3.3: Tag Architecture

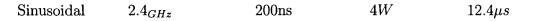

### 3.3 Simulated Reader Signal

The function that generates the signal from the reader, multiplies a 2.4GHz sinusoidal function and a train of pulses that contains the data to implement the protocol. The EIRP (Equivalent Isotropically Radiated Power) considered in the signal is of 4W. The resulting signal is equivalent to the signal that a transponder would see in a given application that corresponds to the architecture of this transponder. The characteristics of the simulated reader are shown in Table 3.1.

Figure 3.4 shows the waveform of the signal in the simulation, and the match with the previously described communication protocol can be verified. The simulation of the complete reader is out of the scope of this job.

Table 3.1: Characteristics of the Reader's Signal

| Type of Signal | Frequency | Duration ( | of the Pulses | EIRP | Total Ti | ime Simulated |

|----------------|-----------|------------|---------------|------|----------|---------------|

|                |           |            |               |      |          |               |

Figure 3.4: Waveform of the Reader's Signal [1]

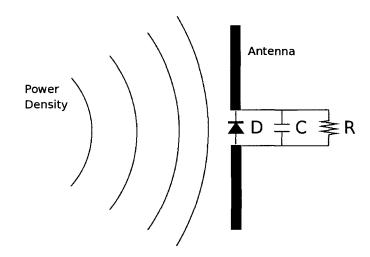

### 3.4 The Rectenna

The rectenna is a special antenna that is used to convert microwave energy into DC electricity. A schematic of a typical rectenna is shown in Figure 3.5. The antenna captures the power from the medium and generates a voltage at the diode access. The latter rectifies the voltage to a DC current that charges the capacitor C at the rate RC.

Figure 3.5: Typical Rectenna Schematic

The rectenna was thoroughly studied starting at the second half of the 20th century resulting in a high overall efficiency systems. With the arrival of the integrated circuit and low power technologies, new applications were possible. In the mid 1980's, RFID appeared in which an inductive or electromagnetic antenna was used for power transmission and communication[20]. All these applications used a block named rectifier, similar to the basic rectenna.

### 3.4.1 Rectifier Building Blocks

The rectifier is built upon two basic electrical circuits, the clamping circuit and the envelope detector circuit.

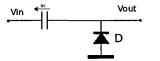

#### 3.4.1.1 Clamping Circuit

The objective of the clamping circuit is to establish a DC reference for the output voltage by using a diode clamp, as shown in Figure 3.6.

Figure 3.6: Diode Clamp Circuit

Conducting whenever the voltage at the output terminal of the capacitor goes negative, the circuit builds an average charge on the terminal that is sufficient to avoid the output from going negative. Positive charge is effectively trapped.

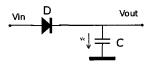

#### 3.4.1.2 Rectifier Circuit

When a voltage is applied to the input of the circuit, the capacitor is charged until its voltage is equal to the maximum input voltage. If no resistor is connected in parallel with the capacitor, the voltage at the output never reduces in theory. In practice the leakage current of the capacitor induces a voltage drop at the output. If the input voltage is a sinusoidal, the capacitor charges every time its voltage is near the peak value and the mean output voltage is a little smaller than the peak amplitude.

Figure 3.7: Basic Rectifier Circuit

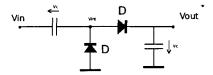

#### 3.4.1.3 The Voltage Doubler

The voltage doubler is obtained by cascading the diode clamping and the rectifier circuit. As seen in Figure 3.8, the circuit outputs a voltage that ideally is twice the amplitude of the input voltage. This circuit is a half wave voltage doubler because only the positive peaks of the input are rectified. To take advantage of the negative and positive peaks in a sinusoidal signal the use of a full-wave rectifier is needed.

Figure 3.8: Voltage Doubler Circuit

The full-wave voltage doubler is just a mirrored circuit with respect to ground of the voltage doubler. In practice, the effects of the elements, diminishes the voltage multiplication. Thus, one has to cascade the circuit, and it results in a Greinacher cascade.

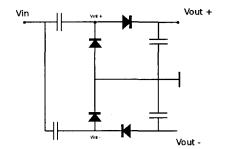

Figure 3.9: Full-Wave Voltage Doubler Circuit

#### 3.4.1.4 Full-wave Greinacher Rectifier

The rectifier offers a good symmetry. It has a low power impedance, low capacitance losses along the RF path to the diodes and reduces the reflected harmonic content. The output voltage is equal to  $4NV_{in}$ , where N is the number of stages[2]. The Greinacher rectifier is described in detail because is the rectifier used in this design, and it is of great importance due its role as a DC voltage supplier.

Figure 3.10: Full-wave Modified Greinacher Circuit [2]

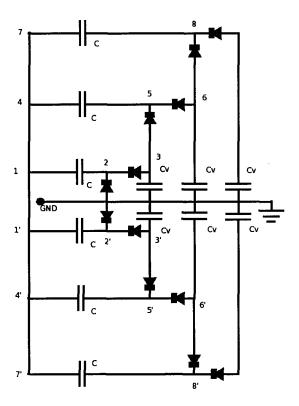

Figure 3.11: Rectifier

25

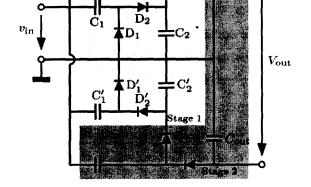

#### 3.4.2 Rectifier

Figure 3.11 shows a three stages Greinacher rectifier. In this simulation the rectifier circuit is conformed by diodes with low threshold voltage, low reverse current and low parasitic capacitance. The considered fabrication material was silicon-on-sapphire because of its low parasitics, low threshold voltage and excellent high frequency performance [21]. The rectifier is a very important block in every remotely powered system. A detailed study of the implemented rectifier is given in [2] and [1].

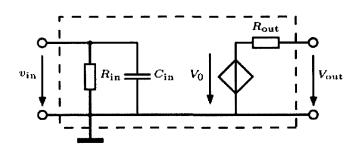

The model in Figure 3.12 allows the prediction of the power needed to supply a given DC output current at a constant DC output voltage.

Figure 3.12: Rectifier Equivalent Circuit [1]

The global rectifier efficiency can be defined as:

$$\eta_0 = \frac{DCOutputPower}{IncidentRFPower} \tag{3.1}$$

#### 3.4.3 Power-on-Reset

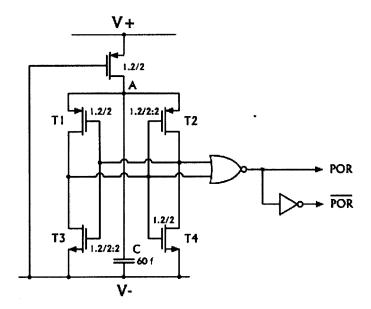

The power-on-reset circuit, as shown in Figure 3.13, is composed of a cross-coupled pair of transistor and a NOR gate and it is a non stable circuit. When the circuit is energized, one transistor takes advantage from the other. The NOR gate compares the two gate signals ensuring a power-on-reset signal for the logic blocks. The capacitor allows node A a slow charging avoiding parasitic oscillation.

Figure 3.13: Power-on-Reset Circuit [1]

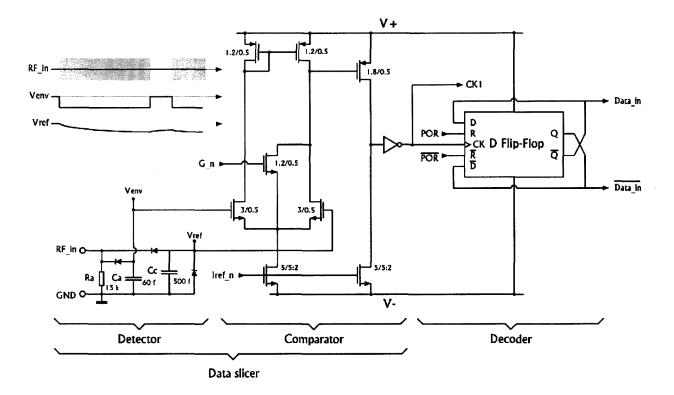

#### 3.4.4 Detector, Data Slicer and Decoder

The detector is formed by an envelope detector and an averaging filter. The outputs are the signals  $V_{env}$  and  $V_{ref}$  that corresponds to the envelope and the rectified average of the received RF signal. Signal  $V_{env}$  is very important because it determines the time to do decoding. When the RF signal increments, the capacitor  $C_a$  charges to the RF envelope. When the signal falls, the capacitor discharges through the resistor  $R_a$ . Because of the inverse current of the diode, the capacitor  $C_a$  discharges sufficiently rapidly. Capacitor  $C_c$  and its touching diodes generates the signal  $V_{ref}$ . When the RF signal rises,  $C_c$  charges down to the half amplitude voltage of the RF envelope signal. When the RF signal falls, the retained voltage of the capacitor slowly reduces due to the inverse current of its parallel diodes that act as a parallel resistance. The data slicer, shown in the Figure 3.14, performs the signal regeneration. The signal  $G_n$  is tied to V<sup>-</sup> during addressing mode. When  $V_{env}$  is higher than  $V_{ref}$ , CK1 rises to a logic "1" and the D flip-flop toggles. After the power-on-reset, the  $Data_{in}$  signal is "0". When one interrumpt in the signal is received, or the start bit is received, signal  $Data_{in}$  toggles from "0" to "1". The start bit is then registered and the rest of the ID of the tag is received. To avoid the detection of undesired bits in the reading mode,

Figure 3.14: Detector, Data Slicer and Decoder Circuit [1]

the data slicer is inhibed when signal  $G_n$  goes high, and as a result CK1 is always low in reading mode.

#### 3.4.5 Shift Register and Logic

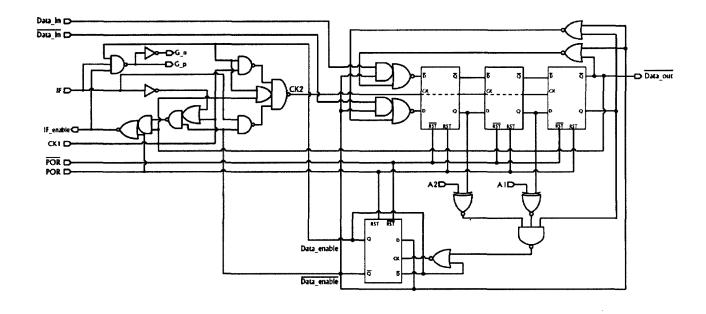

Figure 3.15: Control Unit Circuit [1]

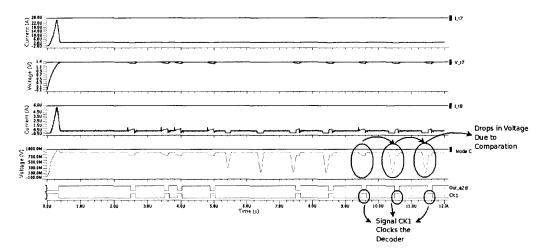

The shift register and logic block is responsible of loading the incoming RF data from the reader,  $Data_{in}$ . The power-on-reset signal start the shift register to a logic "0". In this work three bits shift register is used but it can be increased as desired or and EEPROM can be used to avoid the programming pads. In the addressing mode the signals  $Data_{enable}$  and  $Data_{out}$  are both low. CK2 is equal to the clock frequency. The received data,  $Data_{in}$ , is registered in the shift register on each rising edge of the CK2 signal. The address or ID of a transponder is set with the signals A1 and A2. When the received ID does not match the transponder's ID, the signal  $Data_{enable}$ stays low,  $Data_{out}$  goes high and CK2 = 1, so no further bits are registered in the shift register. Here the transponder goes to the quiet mode. When a matching ID is received,  $Data_{enable}$  goes on and the logic permits the communication with the reader. Signals  $G_n$  and  $G_p$  toggle the ASK modulator between short and open configurations. When the transponder is in the reading mode  $CK2 = C\overline{K1}$  the shift register operates in closed loop, its output goes directly to its input. At each rising edge of CK2, the shift register shifts its bit to the right.

### 3.4.6 System Clock

The transponder needs a clock to synchronize the control logic and the shift register. In [22] a Intermediate Frequency Oscillator is used to achieve this task. In this work, a digital clock is embedded instead of the complete oscillator model. The digital clock, simplifies the design and provides an accurate operation frequency. After testing the transponder operation with the clock, it can be concluded that the replacement is possible with no functionality penalty.

Table 3.2: Characteristics of the System Clock

| riequency Duty Cycle | Frequency | Duty Cycle |

|----------------------|-----------|------------|

|----------------------|-----------|------------|

$1_{MHz}$  0.1

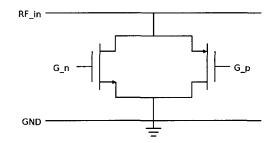

#### 3.4.7 Modulator

Figure 3.16: Parallel Modulator Schematic

The modulator is the key block for the backscattering communication of the transponder. It is responsible for the tag-reader communication by modulating the impedance presented in the transponder's antenna to reflect the modulated power. To maximize the operating range, a low duty-cycle pseudo-PSK RF modulation is implemented[1].Because of this, the modulator can be realized by using just a simple switch. When the switch is open, the reflected power is equal to the difference between the available power from the antenna and the absorbed power. It is dependent of the transponder power consumption. The switch is realized using two MOS transistors in parallel, both controlled by the signals  $G_n$  and  $G_p$ .

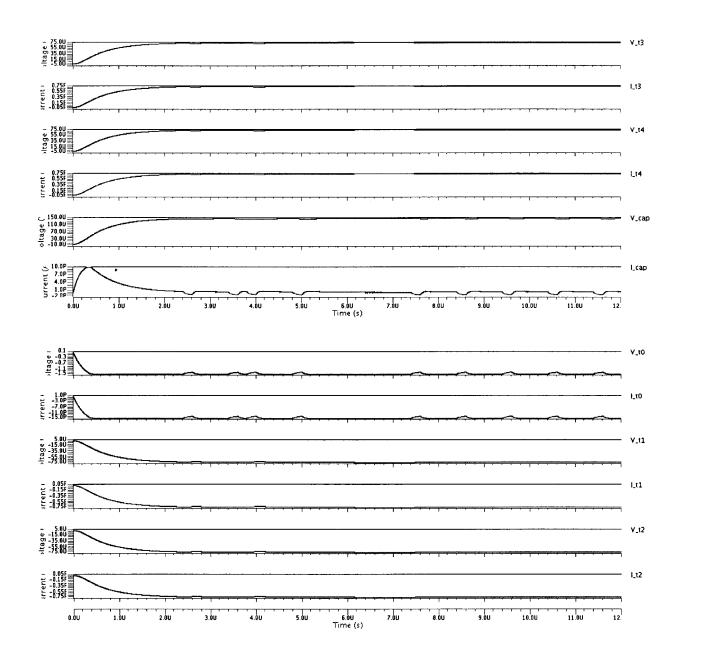

### 3.4.8 Current Reference

Figure 3.17: Current Reference Schematic

The current reference block is used to bias the current used in the different blocks in the circuit. It consists of two PMOS and two NMOS transistors. The transistors T2 and T4 have to work in weak inversion mode. This structure is specially suited for ultra low power applications because a very low current can be obtained by choosing a high value R.

### 3.4.9 Antenna Considerations

The input impedance of the transponder is mainly given by the rectifier. The input impedance is composed by an imaginary part caused by of the parasitic capacitance and by a real part given by the output current consumption. In this work an optimum power transmission from the reader to the transponder is considered, which means that the antenna has a high radiation resistance [2], [23] and an optimum power matching with the transponder circuit. The antenna considered is the 3-wire folded dipole antenna because it helps to raise the value of the radiation resistance. The antenna and power matching strategies goes further from the scope of this work and it could be proposed as a future work.

# Chapter 4

# **Transistor Model**

Modeling and simulation are an important part in the integrated circuits design flow. Modeling the systems on integrated circuits provides a better understanding of the behavior of the chip and the models can be used to create simulations and detect errors even before the chip is fabricated, avoiding the costs of fabrication. During system simulations, the equations that govern the behavior of the system's elements and their interactions are solved by a simulator. A system can be modeled at a transistor level for simulation with more real results. The transistor models cover a large number of linear and non-linear equations that demand large computational times. In order to reduce the time and complexity of the simulations, the compact models are suited for transistor level simulations. The compact models use analytical equations that describe the behavior of the transistors and takes less time to simulate but at the cost of accuracy[24].

# 4.1 MOSFET Model

Metal Oxide Semiconductor Field Effect transistor is a four-terminal device consisting of source, drain, gate and bulk. The voltage applied to the gate terminal determines the quantity of current that flows between the drain and source terminals. There are two types of MOSFET devices: NMOS consists of  $n^+$  drain and source regions embedded in a p-type substrate, the current flow between source and drain is formed by electrons, and PMOS is formed for  $p^+$  drain and source regions in a n-type substrate, the current is carried by holes. This model considers the physical effects of a long channel transistor. For a submicron technology model the mobility effects due to vertical and lateral fields, velocity saturation, short-channel effects as channel-length modulation effects should be considered.

#### 4.1.1 Static Model of MOSFET

The characteristic of a MOS transistor can be divided in three main regions of operation: Cut-off region, Linear region and Saturation region.

#### 4.1.1.1 Cut-off Region

When no gate voltage is applied and drain and source are connected to ground, the drain and source act as a back to back pn-junction which results in an extremely high resistance between source and drain, the current flowing across them is mainly zero.

#### 4.1.1.2 Linear Region

When an applied gate voltage is greater than the threshold voltage and a voltage is applied between drain and source, a current starts to flow between drain and source. The threshold voltage represents the value of the gate voltage where the strong inversion occurs. The threshold voltage is given by

$$V_T = V_{TO} + \gamma \cdot \left(\sqrt{(-2\Phi_F) + V_{SB}} - \sqrt{2\Phi_F}\right) \tag{4.1}$$

$\gamma$  is called the body effect coefficient and  $\Phi_F$  is the Fermi Potential and  $V_{TO}$  represents the threshold voltage for a voltage from source to bulk equal to zero. The current in this region is given by

$$I_D = \mu_n \cdot C_{ox} \cdot (\frac{W}{L}) \cdot [(V_{GS} - V_T) \cdot V_{DS} - \frac{V_{DS}^2}{2}]$$

(4.2)

$\mu$  is the mobility,  $C_{OX}$  is the capacitance of the gate oxide and W, L are the width and length of the transistor.

#### 4.1.1.3 Saturation Region

When the drain to source voltage is increased and  $V_{DS} \ge V_{GS} - V_T$ , the channel thickness is reduced gradually from source to drain, until pinch-off occurs at the drain terminal. The transistor is in the saturation region and the current between drain and source remains constant. The current in this region is given by

$$I_D = \frac{\mu_n C_{OX}}{2} \cdot \frac{W}{L} \cdot (V_{GS} - V_T)^2$$

(4.3)

The last equation suggests that the current remains constant and independent of the voltage applied to the terminals. This is not completely true. The effective channel length is modulated by the voltage applied between drain and source, when this voltage increases the depletion region grows and the effective channel reduces. The next equation describes better the current behavior

$$I_D = I'_D \cdot (1 + \lambda \cdot V_{DS}) \tag{4.4}$$

$I'_D$  is the current expression derived earlier and  $\lambda$  is the empirical parameter called the channel length modulation [25].

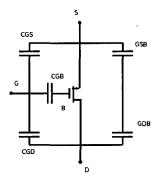

#### 4.1.2 Capacitances

The MOS transistor have some parasitic capacitances between its terminals due the fabrication process. The capacitances can be seen in Figure 4.1. The capacitances can be divided in three major components.

Figure 4.1: MOS Capacitances

#### 4.1.2.1 Overlap Capacitance

The overlap capacitance is generated by the tendency at the source and drain terminals to extend below the oxide of the gate terminal in an amount called lateral diffusion or  $X_d$ .

$$C_{GSO} = C_{GDO} = C_{OX} \cdot X_D \cdot W \tag{4.5}$$

#### 4.1.2.2 Gate to Channel Capacitance

The major component is given by the gate to channel capacitance. These components are given by the region of operation of the transistor. It has three components:  $C_{GCS}$ ,  $C_{GCD}$  and  $C_{GCB}$ . The next table will shows how they behave in the different regions of operation.

Table 4.1: Channel Capacitance in the Different Regions of Operation

| Operation Region | $C_{GCB}$                | $C_{GCS}$                            | $C_{GCD}$                  | $\overline{C_{GC}}$                  |

|------------------|--------------------------|--------------------------------------|----------------------------|--------------------------------------|

| Cutoff           | $C_{OX} \cdot W \cdot L$ | 0                                    | 0                          | $C_{OX} \cdot W \cdot L$             |

| Linear           | 0                        | $C_{OX} \cdot W \cdot L/2$           | $C_{OX} \cdot W \cdot L/2$ | $C_{OX} \cdot W \cdot L$             |

| Saturation       | 0                        | $(2/3) \cdot C_{OX} \cdot W \cdot L$ | 0                          | $(2/3) \cdot C_{OX} \cdot W \cdot L$ |

#### 4.1.2.3 Diffusion Capacitance

The last capacitive component is the diffusion capacitance. This component is caused by the reverse biased current caused by the pn-junctions. It has two components, bottom plate and side wall.

$$C_{diff} = C_{bottom} + C_{side-wall} = C_j \cdot Area + C_{jw} \cdot Perimeter$$

$$(4.6)$$

The parameters used in the transistor of the simulation were taken from [26] and do not correspond to a particular technology but have reasonable values for standard 0.5um CMOS.

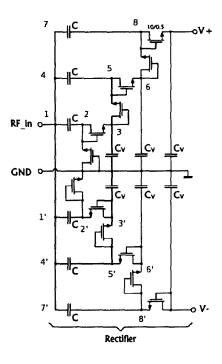

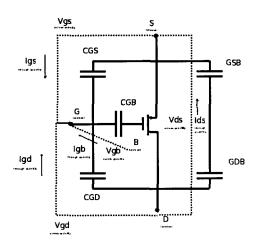

#### 4.1.3 VHDL-AMS Transistor Model

The model included in the simulations was captured by mapping the terminals of the transistor as terminals in the entity of the model. The voltage across the terminals is taken as an across quantity and the currents as a through quantity. The current from drain to source in the different regions is modeled according to the equations 4.1 to 4.4. The parasitic capacitances are also included. Figure 4.2 shows the main quantities of the model and how they are mapped.

Figure 4.2: VHDL AMS Schematic Model

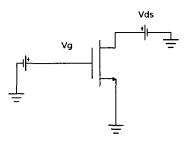

#### 4.1.4 Functional Tests

The next circuits were implemented to verify the behavior of the transistor and for testing its functionality.

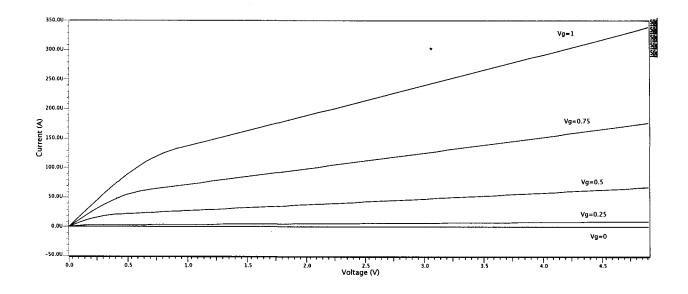

Figure 4.3:  $I_{DS}$  vs  $V_{DS}$  NMOS

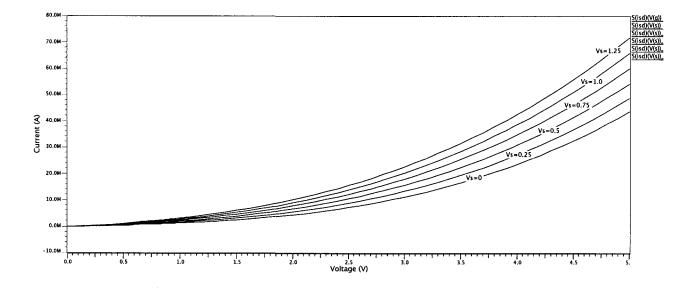

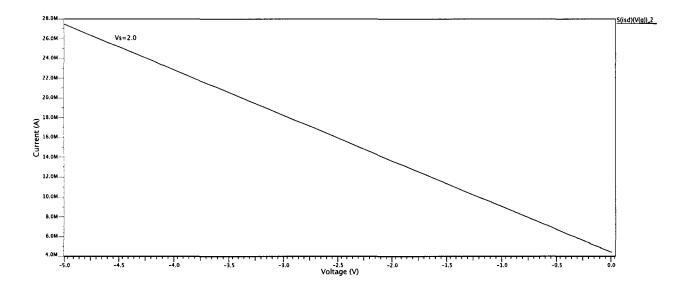

The tests are based on the schematic circuit shown Figure 4.3. First, for test the  $V_{ds} - I_{ds}$  characteristics, a constant voltage at the gate was kept,  $V_g = 1.25V$ , an then a variation in steps of  $10_{mV}$  in the voltage between drain and source was induced,  $V_{ds}$ . The curves in the Figure 4.4 and 4.5 shows the characteristic curves for the NMOS and PMOS transistors used in this work with the given set of parameters. The circuit was simulated in Mentor's Graphics AdvanceMS and the testbench used can be found in Appendix A.

In Figures 4.4 and 4.5 the "X" axis shows the  $V_{ds}$  in the transistor and the "Y"

Figure 4.4:  $I_{DS}$  vs  $V_{DS}$  NMOS

Figure 4.5:  $I_{DS}$  vs  $V_{DS}$  PMOS

axis shows the current  $I_{ds}$ . The circuit was simulated for 5mS.

For test the  $V_{gs} - I_{ds}$  characteristics for the circuit, the voltage  $V_{ds}$  was kept constant and a variation in steps of 10mV in the  $V_g$  voltage was induced. The simulation result graphics have the same characteristics than the ones in Figures 4.4 and 4.5.

Figure 4.6:  $I_{DS}$  vs  $V_{GS}$  NMOS

In Figures 4.6 and 4.7 that the "Y" axis represents the current  $I_{ds}$  and in the "X" axis the voltage  $V_g$  is represented. It can be observed that for a major  $V_g$  a greater  $I_{DS}$  current is flowing from drain to source. The testbench used for this simulation is available in Appendix A.

Based on the tests made to the transistor, it is concluded that the transistor has an acceptable performance for the simulations.

Figure 4.7:  $I_{DS}$  vs  $V_{GS}$  PMOS

40

# Chapter 5

# Results

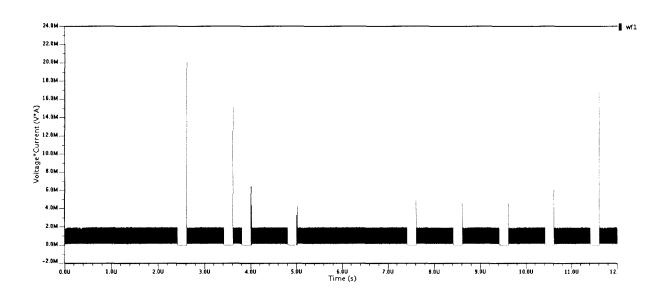

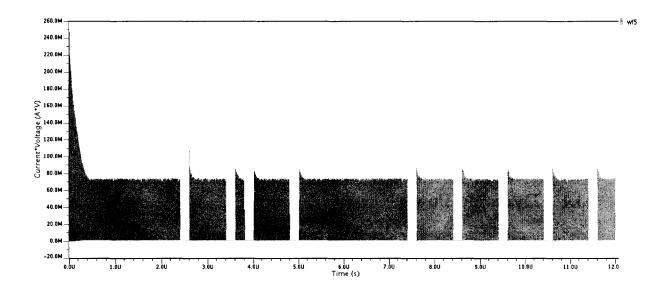

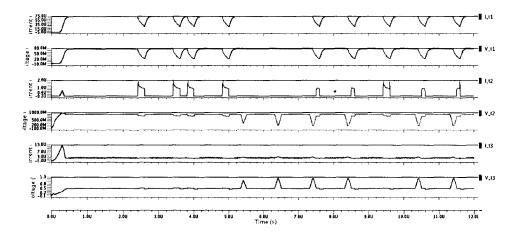

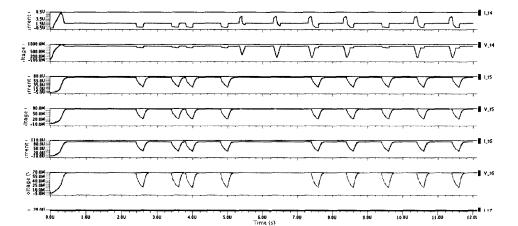

This chapter presents the simulations result of the tag architecture described in section 3.2. The presented results are conformed by the signals that confirm the correct functional behavior of the tag model. It is shown how the signals fulfill the communication protocol described in section 3.1. The total power consumption, obtained by adding the individual power consumption of the subsystems in the tag, and its comparison with other efforts is presented too.

# 5.1 Module's Signals

The signals of each module are presented under two operation conditions: the address sent to the tag matches the own tag's address, and the sent address does not match the tag's address. The difference between the two cases can be appreciated in the signals of the control unit block.

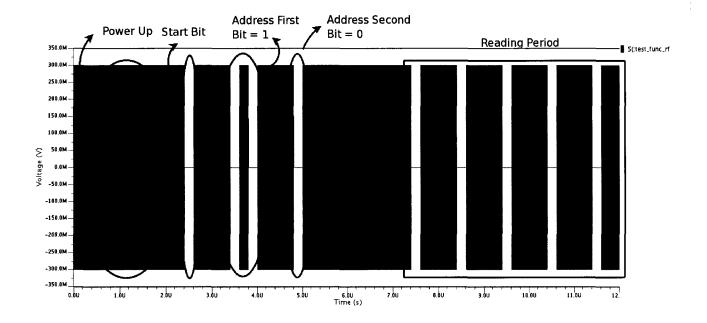

#### 5.1.1 Incident RF Signal

Figure 5.1 shows the RF signal at the antenna of the transponder. As commented in section 3.4.9, an optimum power transmission is considered between the reader and the transponder. The signal match the communication protocol described in section 3.1. In the wave form of the signal a power-up period, that is necessary to energize the circuit, can be seen. An addressing period that sends the start bit and the address of the tag that the reader wants to access. In this simulation the bits sent by the reader are 1-1-0. At the end is the reading period where short interrupts clock the shift register of

Figure 5.1: RF Signal Received by the Transponder

the transponder. Five interrupts are sent in the simulation. The transponder receives the signal, converts it to DC current, stores the power in its capacitors and decodes the information in it. The signal was obtained at the output of the simulated reader module explained in section 3.3.

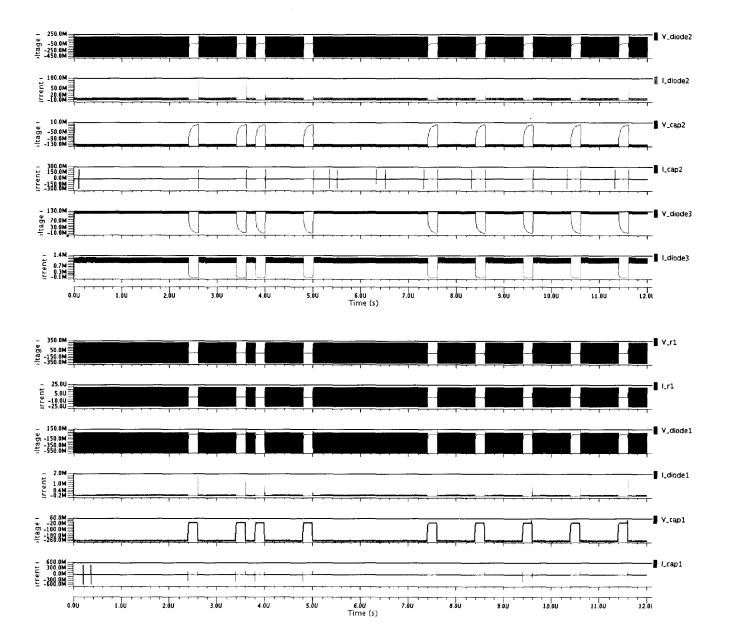

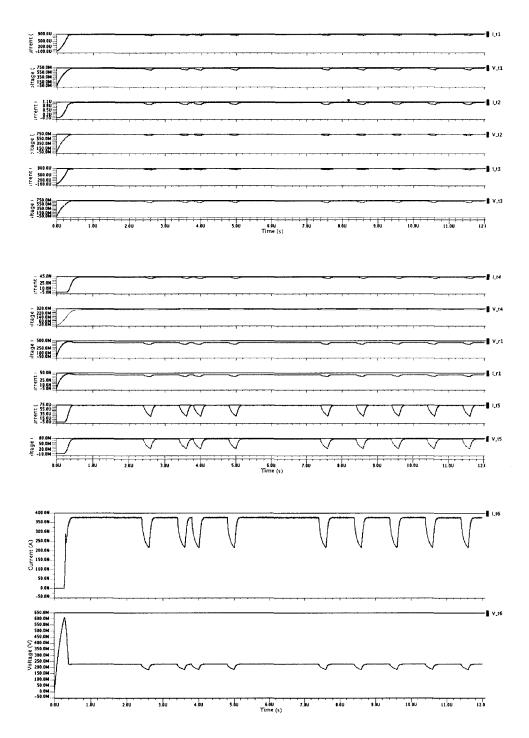

#### 5.1.2 Rectifier

Figure 5.2 shows how the rectifier was implemented in this simulation. The difference between the rectifier showed in Figure 5.2 and the explained in section 3.4.2 is that the transistor model was replaced with an ideal diode model in order to simplify the circuit and to reduce the simulation time. The threshold voltage of the diodes is 0.1V and the capacitance of the capacitors is equal to 100pF, this value allows to the capacitor to charge quickly enough and have a good peak voltage.

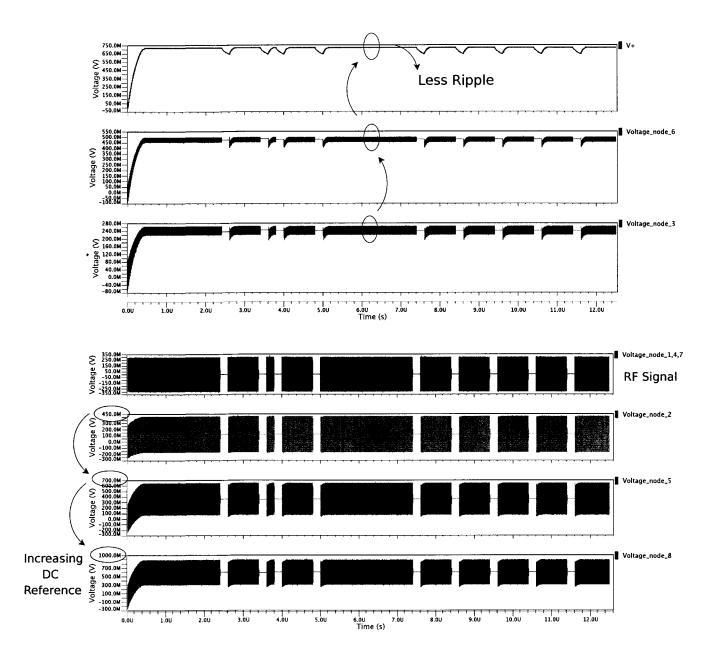

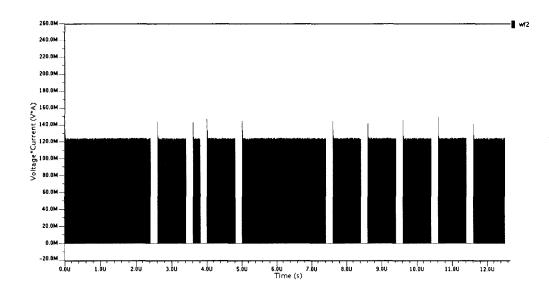

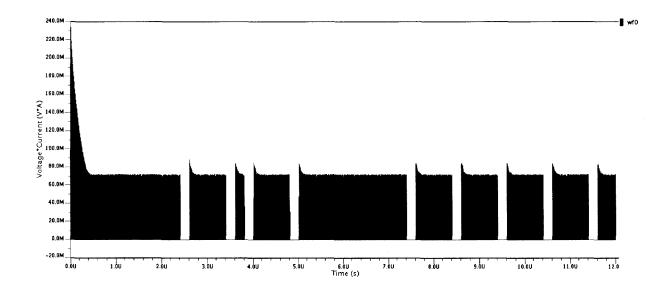

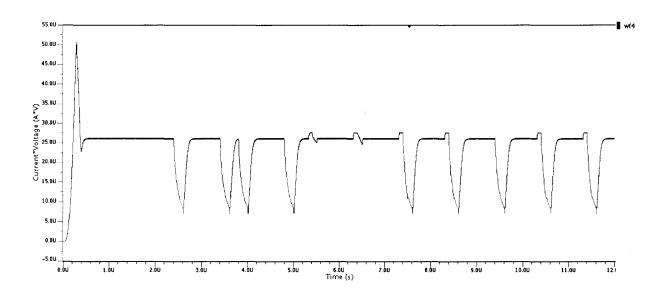

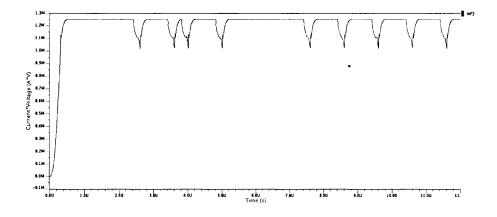

Figure 5.3 shows the node voltages of the positive side of the full-wave rectifier incorporated to the simulation. The voltages in Figure 5.3a) shows how the voltage increments its DC reference on each stage of the rectifier. The increment is due to the effect of the clamping circuit. The clamping circuit conducts every time the voltages at nodes 2, 5 and 8 are negative and builds and average charge that prevents the output

Figure 5.2: Rectifier Implemented in This Simulation

(b) Rectifying the Positive Voltage

(a) Increasing Positive DC Reference

45

(a) Increasing Negative DC Reference

from going negative. In Figure 5.3b), it can be seen how the voltage is being rectified for the rectifier circuit because of the diminishing magnitude of the ripple at each stage. The voltage at node 3 is the output of the first stage of the rectifier. This voltage is added to the output of the clamping circuit in second stage, node 5, to increment its DC reference voltage. The same happens from second to third stage, voltage at node 6 is added to voltage at node 8. The output voltage of the third positive stage is the rectifier's output, V+. The same principles are observed in Figure 5.4, the increment of the negative DC reference is observed in Figure 5.4 a), the outputs of each negative stage of the rectifier are shown in Figure 5.4 b). V- is the negative output of the rectifier.

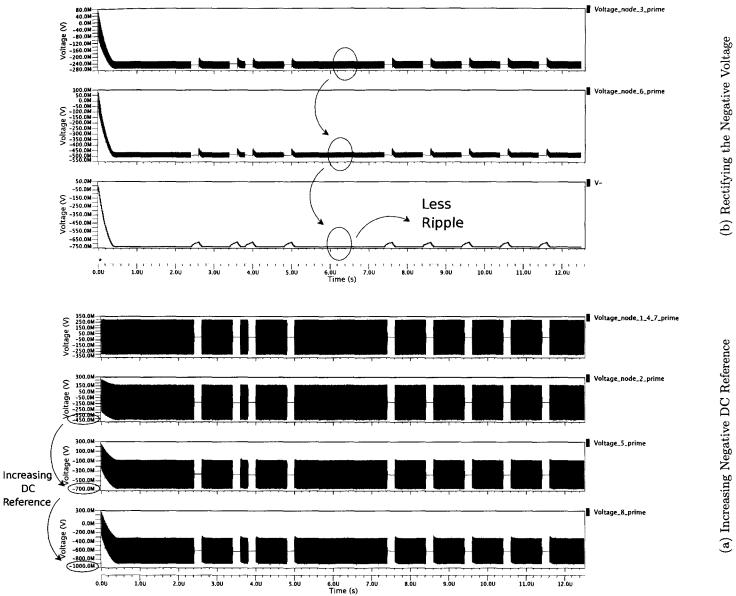

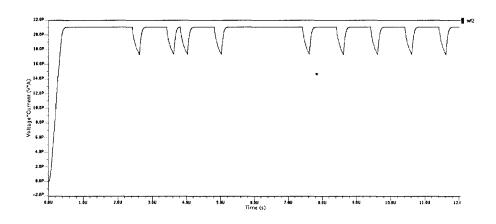

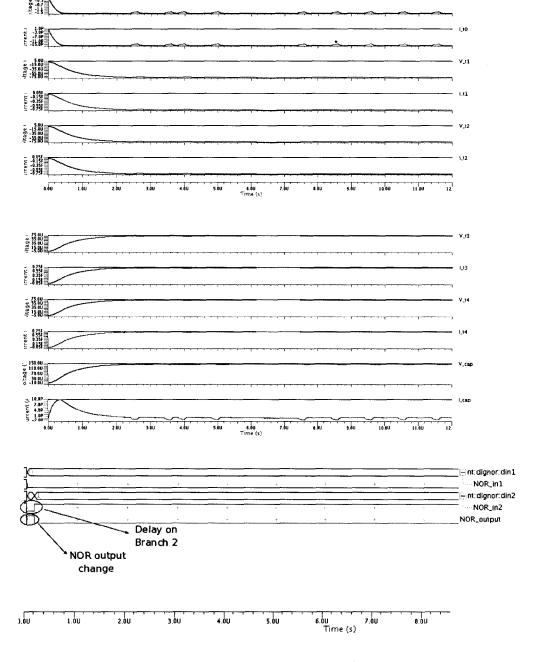

#### 5.1.3 Power-on-Reset

Figure 5.5: Power-on-Reset Simulation Schematic

The schematic of the power-on-reset block (PoRB) is observed in Figure 5.5. The PoRB is responsible to trigger all the blocks in the transponder. In the original design is a non-stable circuit but in this simulation some modifications were done. In the real analog design, the PoRB is a non-stable circuit; however, one branch of the system

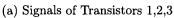

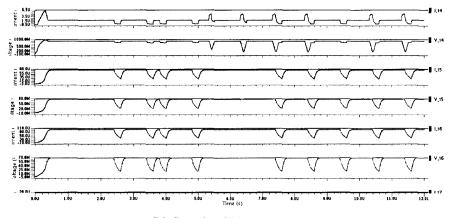

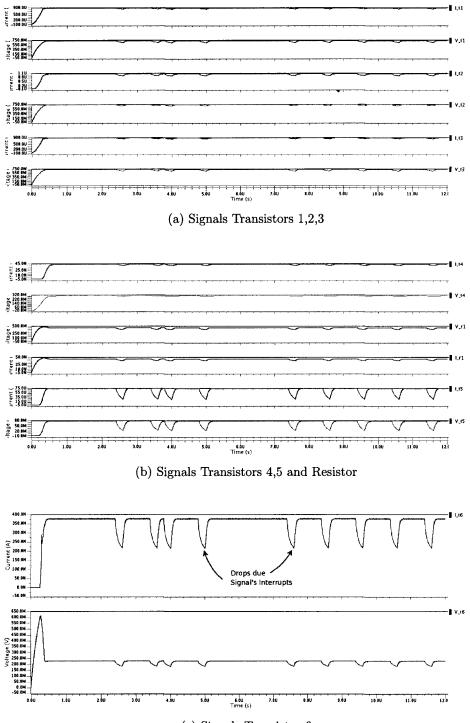

(b) Signals Transistors 3,4 and Capacitor Signals