# INSTITUTO TECNOLÓGICO Y DE ESTUDIOS SUPERIORES DE MONTERREY

### **MONTERREY CAMPUS**

GRADUATE PROGRAM IN MECHATRONICS AND INFORMATION TECHNOLOGIES

## DESIGN OF AN ANALOG CMOS INTERFACE FOR RESONANT MICROSENSORS

### THESIS

PRESENTED AS A PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF SCIENCE WITH MAJOR IN ELECTRONIC ENGINEERING

(ELECTRONIC SYSTEMS)

BY

### LUIS ERNESTO SARACHO MARTÍNEZ

MONTERREY, N.L., MÉXICO. MAY, 2008

# INSTITUTO TECNOLÓGICO Y DE ESTUDIOS SUPERIORES DE MONTERREY

#### **MONTERREY CAMPUS**

### GRADUATE PROGRAM IN MECHATRONICS AND INFORMATION TECHNOLOGIES

The members of the thesis committee hereby approve the thesis of Luis Ernesto Saracho Martínez as a partial fulfillment of the requirements for the degree of Master of Science with major in

> Electronic Engineering (Electronic Systems)

**Thesis Committee**

Graciano Dieck Assad, Ph.D. Thesis Advisor

Sergio O. Martínez C., Ph.D. Thesis Reader

Alfonso Ávila Ortega, Ph.D. Thesis Reader

Joaquín Acevedo, Ph.D. Director of the Graduate Programs in Engineering May, 2008

# DESIGN OF AN ANALOG CMOS INTERFACE FOR RESONANT MICROSENSORS

BY

# LUIS ERNESTO SARACHO MARTÍNEZ

### THESIS

PRESENTED TO THE GRADUATE PROGRAM IN MECHATRONICS AND INFORMATION TECHNOLOGIES

THIS THESIS IS A PARTIAL REQUIREMENT FOR THE DEGREE OF MASTER OF SCIENCE WITH MAJOR IN

> ELECTRONIC ENGINEERING (ELECTRONIC SYSTEMS)

# INSTITUTO TECNOLÓGICO Y DE ESTUDIOS SUPERIORES DE MONTERREY

**MONTERREY CAMPUS**

MAY, 2008

A mi familia...

# Acknowledgements

I want to thank my thesis advisor, Dr. Graciano Dieck Assad, for all of his help and support during the completion of this thesis and throughout my master studies, for sharing his knowledge and letting me grow professionally and as a person.

I would also like to acknowledge the help of my thesis readers, Dr. Sergio Omar Martínez and Dr. Alfonso Ávila, whose valuable teaching during my studies helped me for the realization of this thesis work. Moreover, the time they took from their schedule to review my thesis is greatly appreciated.

I want to thank my family for their love and support. Thank you, mom and dad, this work is the result of your never-ending support and love. Thank you, Aunt Eva and Mr. Luis, for being the greatest grandparents anyone could ask for. Thank you "Jefe" and Patto, for being there when I need it. You know that you can always count on me.

Special thanks to M.S. Alfredo Farid Bautista, M.S. Carlos Díaz, M.S. Luis Valencia and M.S. Zaira Pineda, whose work and advice found the basis of my research. And whose frienship helped me to find my space in the Most Entertaining Place in the World: *LabMEMS*.

Thanks to Israel, other Israel, other-other Israel, "Vatito", M&M, Ever, Brother, Manuel, Juan-which Juan?, Juanpi, Melipa, Norita, Marco, Marco Polo, Esther, Erick, Bere-nice, Edith, and to my fellows of the caving club. I wouldn't have finished without your help and friendship.

#### LUIS ERNESTO SARACHO MARTÍNEZ

Instituto Tecnológico y de Estudios Superiores de Monterrey May 2008

### DESIGN OF AN ANALOG CMOS IC INTERFACE FOR BIOMEMS SENSOR APPLICATIONS

Luis Ernesto Saracho Martínez, M.S.

Instituto Tecnológico y de Estudios Superiores de Monterrey, 2008

Thesis Advisor: Graciano Dieck Assad, Ph.D.

### Abstract

The aim of this thesis is to design a CMOS analog integrated circuit for conditioning a MEMS sensor frequency signal of up to 100 kHz, with an amplitude up to 1  $\mu V_{p}$ . The circuit is designed with the CMOS AMS® 0.35  $\mu m$  technology process parameters.

In order to facilitate the design process, a modular methodology is used. The design starts with the requirements of the complete system, such as gain, bandwidth, power dissipation, etc., and follows with the schematic design of each individual stage.

The amplifier design is based on the synthesis of an OTA device which meets signal specifications of typical MEMS transducers for both, frequency and level voltage inputs, which are around 50 kHz, and 10  $\mu V_p$ , respectively. Analytical and simulation results show differences of less than 10 % in the instrumentation amplifier gain, less than 5 % in the gain bandwidth approximation, and less than 7 % in the slew rate parameter for the instrumentation amplifier and the associated devices of the frecuency signal conditioning circuit designed for MEMS resonant sensors. The simulation analysis of all stages is performed in both, individual fashion and also in integrated form to verify the complete system operation of the frequency conditioning monitor circuit.

Finally, this thesis develops the layout of the circuit, following the same modular methodology, and obtaining reusable modules of the synthesized CMOS stages.

# Contents

| A        | ckno  | wledge  | ements                             | i   |

|----------|-------|---------|------------------------------------|-----|

| A        | bstra | nct     |                                    | iii |

| 1        | Inti  | oduct   | ion                                | 1   |

|          | 1.1   | Proble  | em Statement                       | 1   |

|          | 1.2   | Objec   | tives                              | 2   |

|          | 1.3   | Previo  | ous Work                           | 3   |

|          | 1.4   | Thesis  | s Outline                          | 5   |

| <b>2</b> | Pri   | nciples | s of Analog Circuit Design         | 6   |

|          | 2.1   | Introd  | luction                            | 6   |

|          | 2.2   | The N   | MOS Transistor                     | 6   |

|          |       | 2.2.1   | Operating Regions                  | 8   |

|          |       | 2.2.2   | Large-Signal Model                 | 9   |

|          |       | 2.2.3   | Linear Characteristics             | 11  |

|          |       | 2.2.4   | Small-Signal Model                 | 11  |

|          | 2.3   | Single  | e Stage Amplifiers                 | 13  |

|          |       | 2.3.1   | Current-Source Inverter            | 14  |

|          |       | 2.3.2   | Push-pull Inverter                 | 15  |

|          |       |         | CMOS Inverter Design Methodology   | 16  |

|          |       | 2.3.3   | Differential Amplifier             | 17  |

|          |       |         | Large-Signal Analysis              | 17  |

|          |       |         | Small-Signal Analysis              | 18  |

|          | 2.4   | Opera   | ational Transconductance Amplifier | 19  |

|          |       | 2.4.1   | The $g_m/I_D$ Design Methodology   | 20  |

|   | 2.5 | MOS     | Device Layout                             | 21 |

|---|-----|---------|-------------------------------------------|----|

|   |     | 2.5.1   | MOS Transistor Layout                     | 21 |

|   |     | 2.5.2   | MOS Resistor Layout                       | 22 |

|   |     | 2.5.3   | Capacitor Layout                          | 24 |

|   |     | 2.5.4   | Layout Design Rules                       | 24 |

|   |     | 2.5.5   | General Matching Concepts                 | 25 |

|   |     |         | Floorplaning                              | 25 |

|   |     |         | Geometry                                  | 27 |

|   |     |         | General Matching Rules                    | 29 |

| 3 | Mic | crosyst | ems                                       | 30 |

|   | 3.1 | Introd  | luction                                   | 30 |

|   | 3.2 | Defini  | tion of MEMS                              | 30 |

|   | 3.3 | Physic  | cs of Silicon                             | 31 |

|   |     | 3.3.1   | Single Crystal Silicon                    | 31 |

|   |     | 3.3.2   | Polycrystalline Silicon                   | 31 |

|   |     | 3.3.3   | Electrical properties                     | 32 |

|   |     | 3.3.4   | Mechanical properties                     | 33 |

|   |     | 3.3.5   | Piezoresistivity                          | 34 |

|   | 3.4 | Piezor  | resistive Sensors                         | 35 |

|   |     | 3.4.1   | Wheatstone Bridge Configuration           | 35 |

|   |     | 3.4.2   | Operation Modes of Piezoresistive Sensors | 36 |

|   |     |         | Applications of Piezoresistive Sensors    | 38 |

| 4 | Sig | nal Co  | nditioning Circuit Design                 | 42 |

|   | 4.1 | Introd  | luction                                   | 42 |

|   | 4.2 | Opera   | tional Transconductance Amplifier         | 43 |

|   |     | 4.2.1   | General Requirements                      | 43 |

|   |     | 4.2.2   | Differential Pair Stage                   | 45 |

|   |     | 4.2.3   | Current-Source Load Stage                 | 49 |

|   |     | 4.2.4   | Requirements Comparison                   | 51 |

|   |     |         | Output Voltage Range                      | 51 |

|   |     |         | Power Consumption                         | 52 |

|   |     |         | Gain                                      | 53 |

|   |      | 4.2.5   | Right Half-Plane Zero Compensation            | 53 |

|---|------|---------|-----------------------------------------------|----|

|   |      | 4.2.6   | Iteration Process                             | 53 |

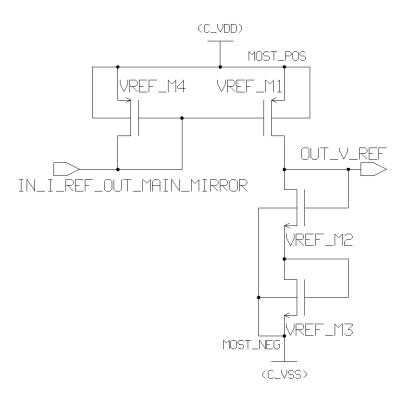

|   |      | 4.2.7   | Bias Voltage Circuit                          | 56 |

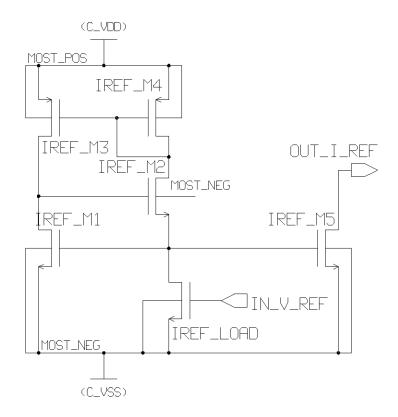

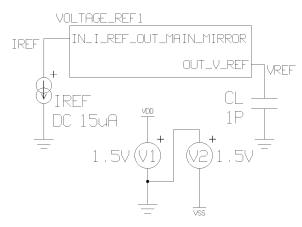

|   |      | 4.2.8   | Bias Current Circuit                          | 60 |

|   |      | 4.2.9   | System Modularization                         | 65 |

|   |      |         | Differential Pair Circuit                     | 65 |

|   |      |         | Modified Differential Pair Circuit            | 65 |

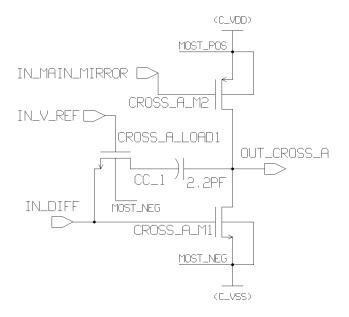

|   |      |         | Current-Source Load Circuit                   | 67 |

|   |      |         | Bias Voltage Circuit                          | 67 |

|   |      |         | Bias Current Circuit                          | 70 |

|   |      | 4.2.10  | OTA Packaging                                 | 70 |

|   | 4.3  | Instru  | mentation Amplifier                           | 72 |

|   |      | 4.3.1   | Theoretical Design                            | 73 |

|   |      | 4.3.2   | Practical Design                              | 74 |

|   |      | 4.3.3   | Passive Components Replacement                | 74 |

|   |      | 4.3.4   | IA Packaging                                  | 78 |

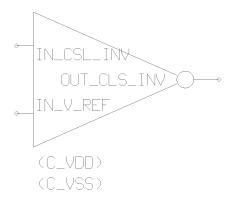

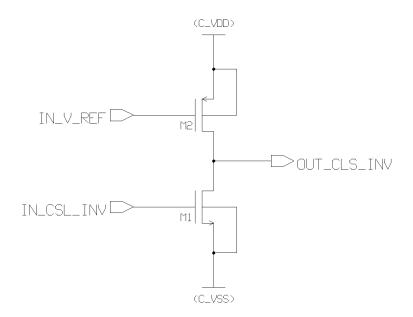

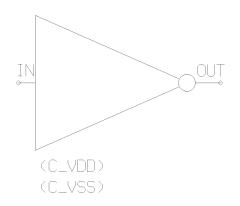

|   | 4.4  | Inverte | er Amplifier                                  | 78 |

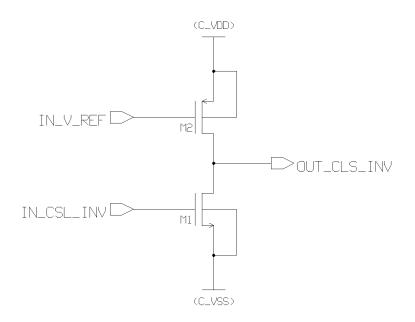

|   |      | 4.4.1   | Current-Source Inverter Amplifier             | 80 |

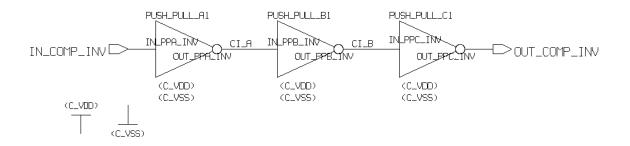

|   |      | 4.4.2   | Triple Push-Pull Inverter and Symbol Creation | 82 |

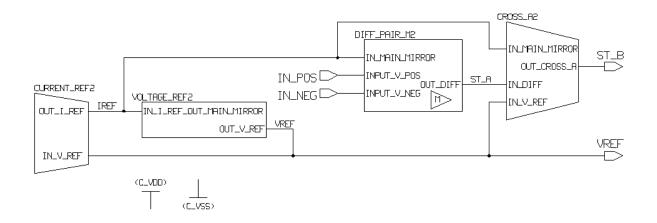

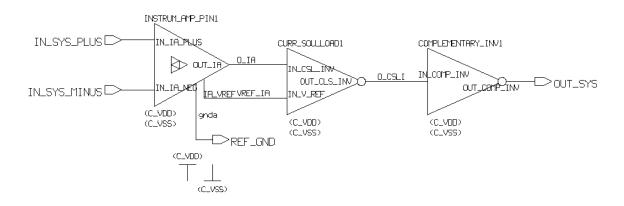

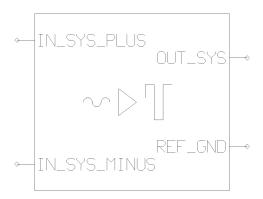

|   | 4.5  | Signal  | Conditioning Circuit                          | 85 |

|   |      | 4.5.1   | Modules Integration                           | 85 |

|   |      | 4.5.2   | Signal Conditioning Circuit Packaging         | 85 |

| 5 | Cire | cuit Si | mulation and Testing                          | 88 |

|   | 5.1  | Introd  | uction $\ldots$                               | 88 |

|   | 5.2  | OTA S   | Simulation                                    | 88 |

|   |      | 5.2.1   | Bias Voltage Circuit Time Response            | 89 |

|   |      | 5.2.2   | Bias Current Circuit Time Response            | 39 |

|   |      | 5.2.3   | OTA Frequency Response                        | 91 |

|   |      | 5.2.4   | OTA Voltage Response                          | 92 |

|   |      | 5.2.5   | OTA Time Response                             | 94 |

|   | 5.3  | Instru  | mentation Amplifier Simulation                | 95 |

|   |      | 5.3.1   | IA Frequency Response                         | 96 |

|   |      | 5.3.2   | IA Voltage Response                           | 98 |

| <ul> <li>5.4.1 Curren</li> <li>5.4.2 Curren</li> <li>5.4.3 Curren</li> <li>5.4.4 Triple</li> </ul> | lifier Module Simulation                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul><li>5.4.2 Curren</li><li>5.4.3 Curren</li><li>5.4.4 Triple</li></ul>                           | at-Source Inverter Voltage Response                                                                                                                                                                                                                                                                                                                  |

| 5.4.3 Curren<br>5.4.4 Triple                                                                       | t-Source Inverter Time Response                                                                                                                                                                                                                                                                                                                      |

| 5.4.4 Triple                                                                                       | -                                                                                                                                                                                                                                                                                                                                                    |

| -                                                                                                  | Push-Pull Inverter Voltage Response                                                                                                                                                                                                                                                                                                                  |

| Signal Condit                                                                                      |                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                    | ioning System Simulation                                                                                                                                                                                                                                                                                                                             |

| 5.5.1 System                                                                                       | h Frequency Response $\ldots \ldots 1$                                                                                                                                                                                                                                                |

| 5.5.2 System                                                                                       | n Voltage Response $\ldots \ldots 1$                                                                                                                                                                                                                                           |

| 5.5.3 System                                                                                       | Time Response $\ldots \ldots 1$                                                                                                                                                                                                                           |

| 5.5.4 Discus                                                                                       | sion of Simulation Results                                                                                                                                                                                                                                                                                                                           |

| out Design                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                    |

| Introduction .                                                                                     |                                                                                                                                                                                                                                                                                                                                                      |

| Inverter Push                                                                                      | Pull Inverter                                                                                                                                                                                                                                                                                                                                        |

| Current-Source                                                                                     | e Inverter Amplifier                                                                                                                                                                                                                                                                                                                                 |

| Operational T                                                                                      | ransconductance Amplifier                                                                                                                                                                                                                                                                                                                            |

| 6.4.1 Differe                                                                                      | ntial Pair Circuit                                                                                                                                                                                                                                                                                                                                   |

| 6.4.2 Curren                                                                                       | t-Source Load Circuit                                                                                                                                                                                                                                                                                                                                |

| 6.4.3 Bias V                                                                                       | oltage Circuit                                                                                                                                                                                                                                                                                                                                       |

| 6.4.4 Bias C                                                                                       | urrent Circuit                                                                                                                                                                                                                                                                                                                                       |

| 6.4.5 OTA I                                                                                        | $ayout \dots \dots$                                                                                                                                                                                                                            |

| Instrumentati                                                                                      | on Amplifier                                                                                                                                                                                                                                                                                                                                         |

| 6.5.1 IA Con                                                                                       | mplete Layout Design                                                                                                                                                                                                                                                                                                                                 |

| 6.5.2 Transr                                                                                       | esistances Placement                                                                                                                                                                                                                                                                                                                                 |

| Signal Condit                                                                                      | ioning Circuit                                                                                                                                                                                                                                                                                                                                       |

| 6.6.1 Summ                                                                                         | ary                                                                                                                                                                                                                                                                                                                                                  |

| nclusions and                                                                                      | Future Work 13                                                                                                                                                                                                                                                                                                                                       |

| Conclusions                                                                                        |                                                                                                                                                                                                                                                                                                                                                      |

| Future Work                                                                                        |                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                    | 5.5.3 System<br>5.5.4 Discus<br>yout Design<br>Introduction<br>Inverter Push-<br>Current-Source<br>Operational T<br>6.4.1 Differe<br>6.4.2 Curren<br>6.4.3 Bias V<br>6.4.4 Bias C<br>6.4.3 Bias V<br>6.4.4 Bias C<br>6.4.5 OTA I<br>Instrumentation<br>6.5.1 IA Con<br>6.5.2 Transr<br>Signal Condit<br>6.6.1 Summa<br>onclusions and<br>Conclusions |

| В  | Scri  | pts Used for Design Methodology             | 142 |

|----|-------|---------------------------------------------|-----|

|    | B.1   | Octave Script for OTA Stage Design          | 142 |

|    | B.2   | Octave Script for Bias Voltage Stage Design | 153 |

|    | B.3   | Octave Script for Bias Current Stage Design | 158 |

| Bi | bliog | raphy                                       | 161 |

| Vi | ta    |                                             | 166 |

# List of Figures

| 2.1  | Physical structure of MOS transistors                                               | 7  |

|------|-------------------------------------------------------------------------------------|----|

| 2.2  | The MOS transistor symbol                                                           | 8  |

| 2.3  | Polarization circuit and $I_D$ response of an n-channel MOS transistor.             | 10 |

| 2.4  | Linear operation in deep triode region [1]. $\ldots$ $\ldots$ $\ldots$ $\ldots$     | 12 |

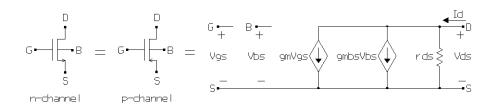

| 2.5  | Small-signal model of the MOS transistor.                                           | 12 |

| 2.6  | Voltage transfer curve and circuit of the current-source inverter [2]. $\therefore$ | 15 |

| 2.7  | Voltage transfer curve and circuit of the push-pull inverter [2]. $\ldots$          | 16 |

| 2.8  | Differential amplifier and its voltage-transfer curve [2]                           | 17 |

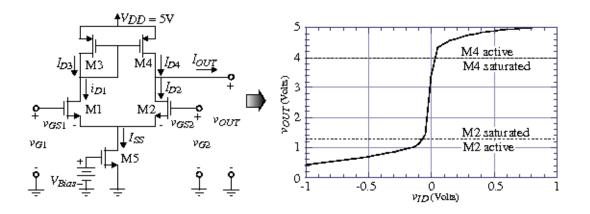

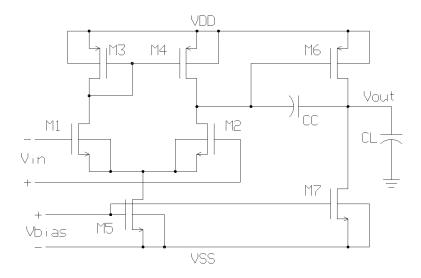

| 2.9  | Unbuffered, two-stage CMOS OTA with an n-channel input pair [2]                     | 20 |

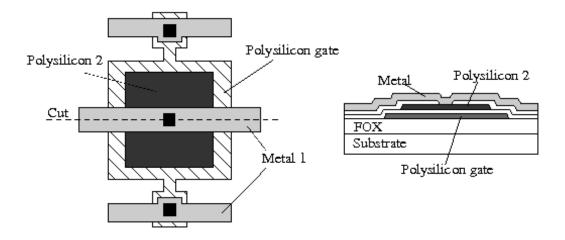

| 2.10 | Top and side view of an n-channel MOS transistor layout.                            | 22 |

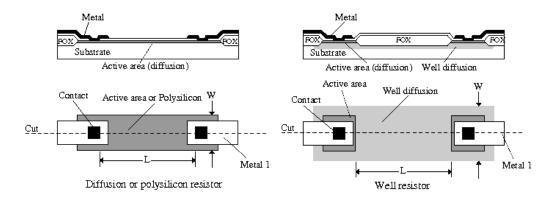

| 2.11 | Layout of a diffusion resistor and a well resistor [2]                              | 23 |

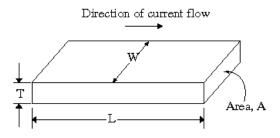

| 2.12 | Current flow in conductive bar $[2]$                                                | 23 |

| 2.13 | Example layout of a double-polysilicon capacitor [2]                                | 24 |

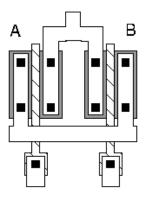

| 2.14 | Unmatched MOS transistor pair [2]                                                   | 26 |

| 2.15 | Example layout of MOS transistors using mirror symmetry [2]                         | 26 |

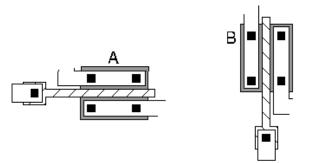

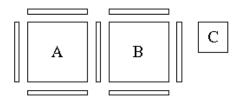

| 2.16 | Matching of A and B is disturbed by the presence of $C$ [2]                         | 27 |

| 2.17 | Improved matching achieved by matching surroundings of $A$ and $B$ [2].             | 27 |

| 2.18 | Two transistors sharing a common source, split in their unit component              |    |

|      | and interdigitated $[2]$                                                            | 28 |

| 2.19 | Compact layout of Figure 2.18 [2]                                                   | 28 |

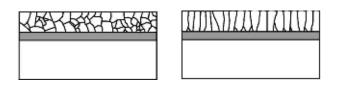

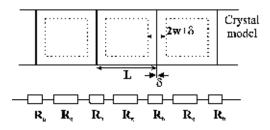

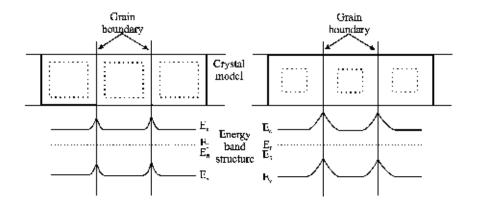

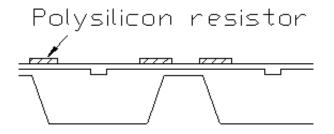

| 3.1  | Two polysilicon structures [3]                                                      | 32 |

| 3.2  | Simple electrical model for polysilicon [3]                                         | 33 |

| 3.3  | Model structure showing the band bending due to the barrier [3]. $\ldots$           | 33 |

| 3.4  | Simple representation of a piezoresistive sensor membrane                           | 36 |

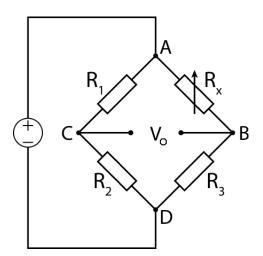

| 3.5  | Wheatstone bridge circuit configuration.                                            | 36 |

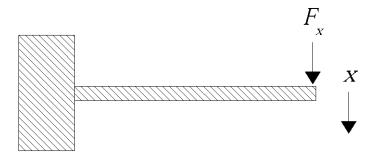

| 3.6  | Deflection of a cantilever beam by a vertical point force, $F_x$ [4] 37           |  |  |

|------|-----------------------------------------------------------------------------------|--|--|

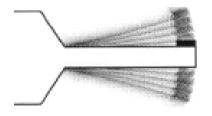

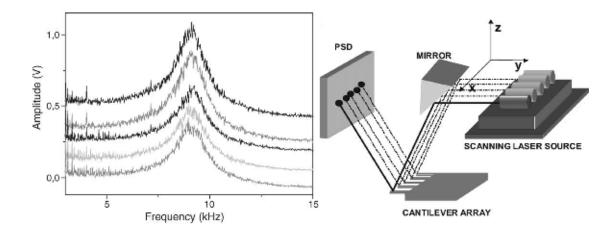

| 3.7  | Schematic of a resonant mass sensor microcantilever [5]                           |  |  |

| 3.8  | Frequency response and system for the sequential readout of microcan-             |  |  |

|      | tilever arrays [6]. $\ldots$ 39                                                   |  |  |

| 3.9  | Components of a MEMS membrane [7]                                                 |  |  |

| 3.10 | Displacement of the membrane shown in Figure 3.9 [7]                              |  |  |

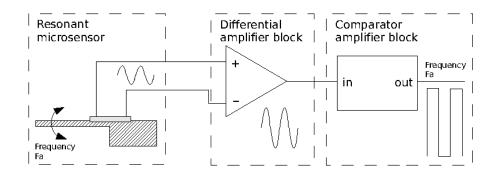

| 4.1  | Block diagram of the complete proposed system                                     |  |  |

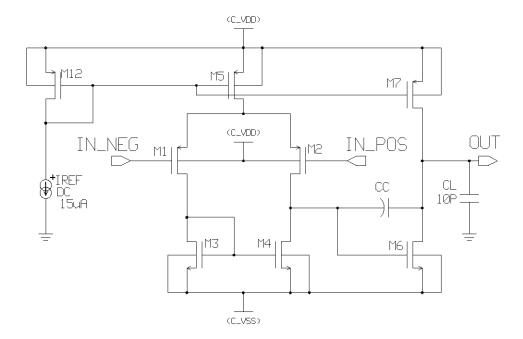

| 4.2  | Unbuffered, two-stage CMOS OTA with a p-channel input pair 45                     |  |  |

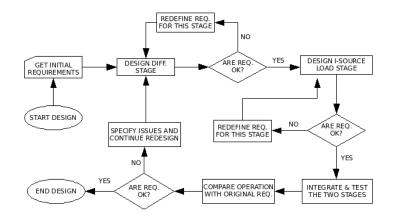

| 4.3  | Flowchart diagram of the OTA design procedure                                     |  |  |

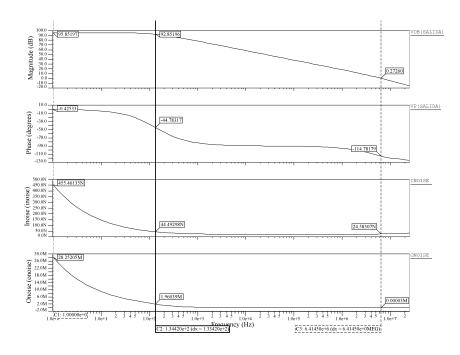

| 4.4  | Frequency response of circuit with parameters from Table 4.4                      |  |  |

| 4.5  | Frequency response of circuit with parameters from Table 4.5                      |  |  |

| 4.6  | CMOS two-stage OTA using nulling resistor compensation                            |  |  |

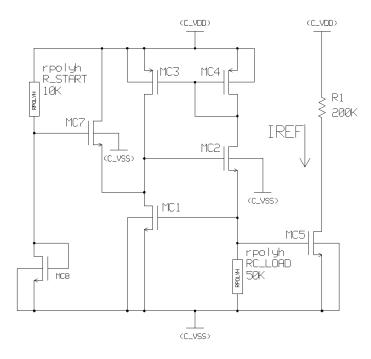

| 4.7  | Bias current circuit                                                              |  |  |

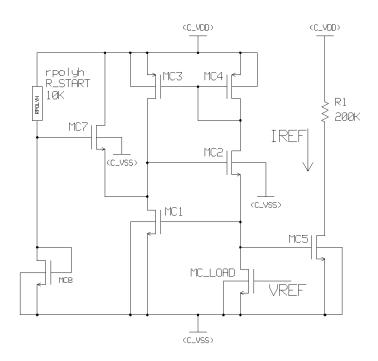

| 4.8  | Bias current circuit with active resistance                                       |  |  |

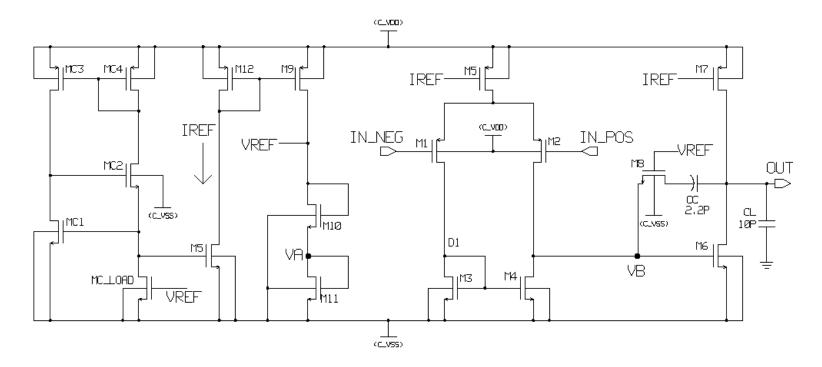

| 4.9  | Complete two-stage CMOS OTA                                                       |  |  |

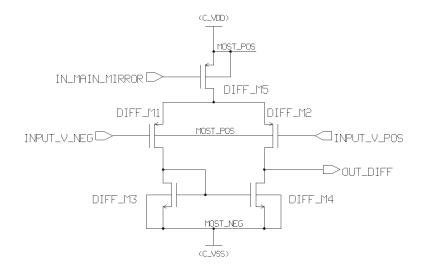

| 4.10 | Differential pair schematic circuit diagram                                       |  |  |

| 4.11 | Differential pair symbol module                                                   |  |  |

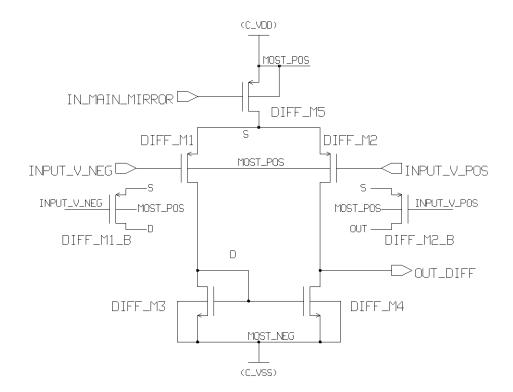

| 4.12 | Modified Differential pair schematic circuit diagram                              |  |  |

| 4.13 | Modified Differential pair symbol module                                          |  |  |

| 4.14 | Current-source load schematic circuit diagram                                     |  |  |

| 4.15 | Current-source load symbol module                                                 |  |  |

| 4.16 | Bias voltage schematic circuit diagram                                            |  |  |

| 4.17 | Bias voltage symbol module                                                        |  |  |

| 4.18 | Bias current schematic circuit diagram                                            |  |  |

| 4.19 | Bias current symbol                                                               |  |  |

| 4.20 | OTA schematic circuit diagram with bias output voltage connection $72$            |  |  |

| 4.21 | OTA symbol module with bias voltage output connection                             |  |  |

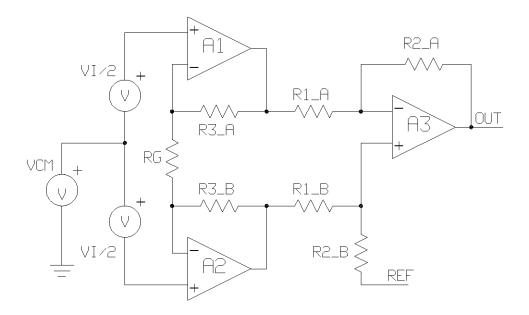

| 4.22 | Triple op-amp IA circuit [8]. $\ldots$ 73                                         |  |  |

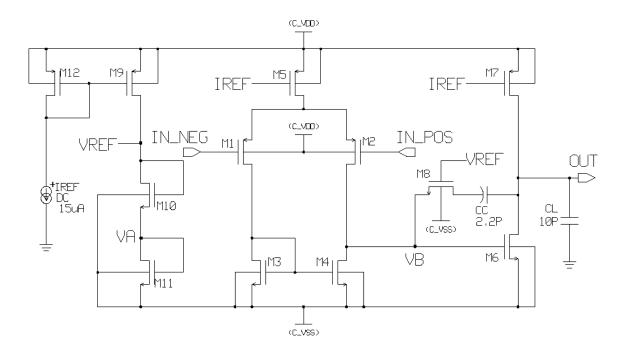

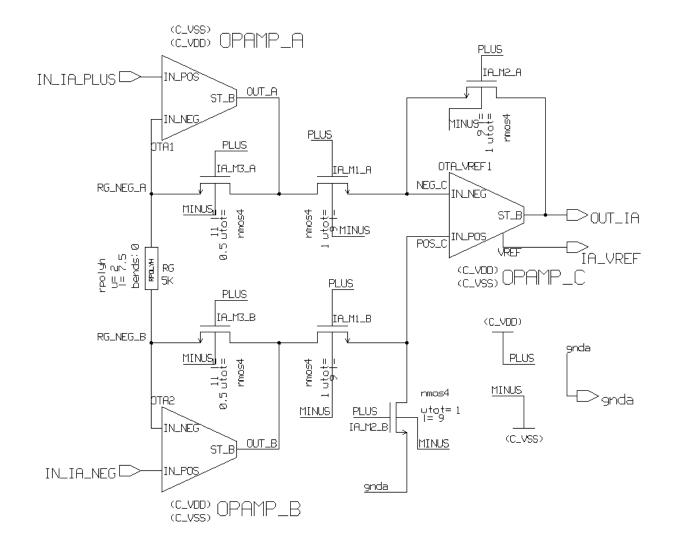

| 4.23 | Design implementation of the IA with gain $A_V \approx 101 \text{ V/V.} \dots 75$ |  |  |

| 4.24 | Frequency response of IA circuit from Figure 4.23                                 |  |  |

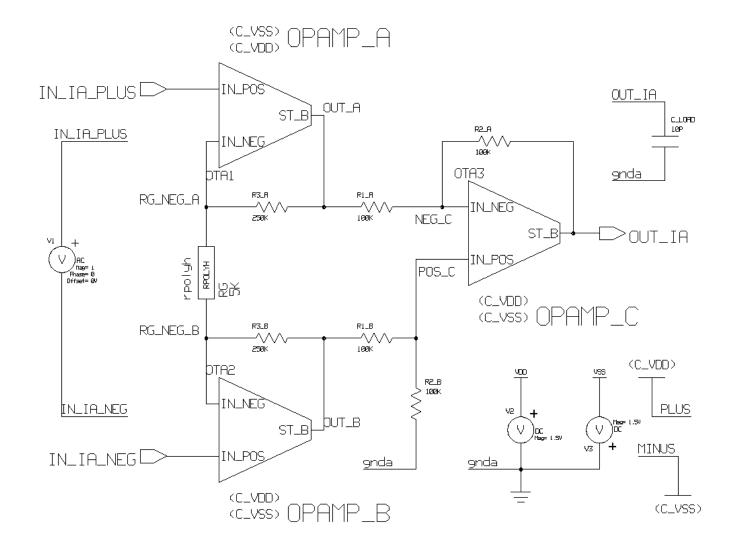

| 4.25 | Modified IA schematic circuit diagram with reference voltage output               |  |  |

|      | connection                                                                        |  |  |

| 4.26 | Frequency response of IA circuit from Figure 4.25                                 |  |  |

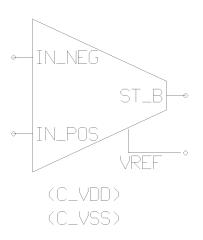

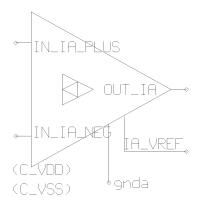

| 4.27 | Five terminal instrumentation amplifier symbol module                     | 79  |

|------|---------------------------------------------------------------------------|-----|

| 4.28 | Current-source inverter schematic diagram                                 | 81  |

| 4.29 | Voltage transfer curve of circuit Figure 4.28                             | 81  |

| 4.30 | Current-source inverter symbol module                                     | 82  |

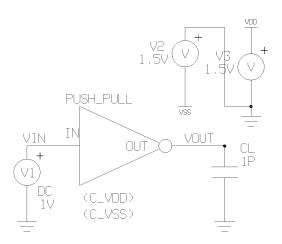

| 4.31 | Schematic circuit diagram for inverter modules A, B, C                    | 83  |

| 4.32 | Individual symbol for inverter modules A, B, C                            | 83  |

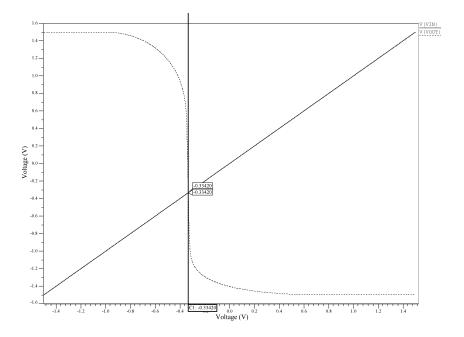

| 4.33 | Voltage transfer curve of the push-pull A inverter amplifier              | 84  |

| 4.34 | Voltage transfer curve of the push-pull B inverter amplifier              | 84  |

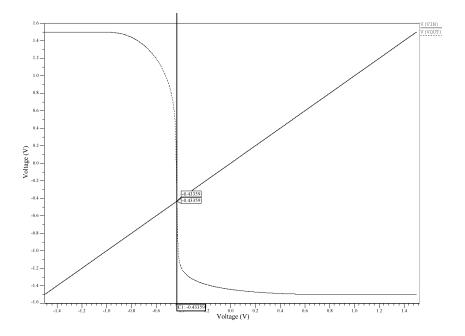

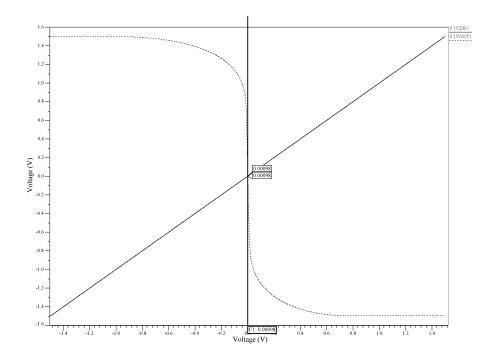

| 4.35 | Voltage transfer curve of the push-pull C inverter amplifier              | 86  |

| 4.36 | Triple inverter schematic circuit diagram                                 | 86  |

| 4.37 | Triple inverter symbol module                                             | 87  |

| 4.38 | Signal conditioning circuit                                               | 87  |

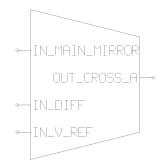

| 4.39 | Signal conditioning circuit symbol.                                       | 87  |

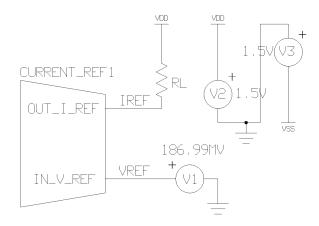

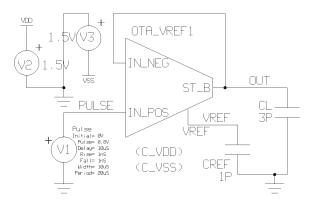

| 5.1  | Circuit configuration for analysing the bias voltage module               | 89  |

| 5.2  | Circuit configuration for testing the bias current module                 | 91  |

| 5.3  | Circuit for testing the OTA's open-loop frequency response                | 92  |

| 5.4  | OTA's frequency response                                                  | 93  |

| 5.5  | OTA's open-loop voltage transfer curve.                                   | 93  |

| 5.6  | Circuit for testing the OTA's time response                               | 94  |

| 5.7  | OTA's Time response.                                                      | 95  |

| 5.8  | Closer view at the rising edge of OTA's time response                     | 96  |

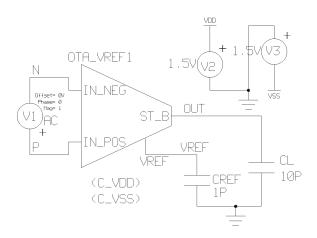

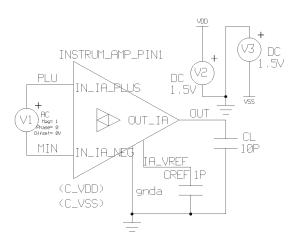

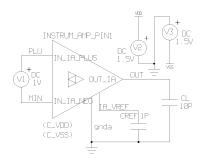

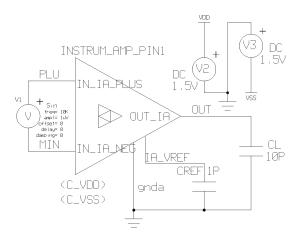

| 5.9  | Circuit configuration for testing the IA's frequency response             | 97  |

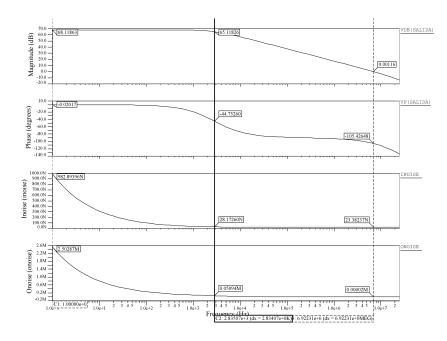

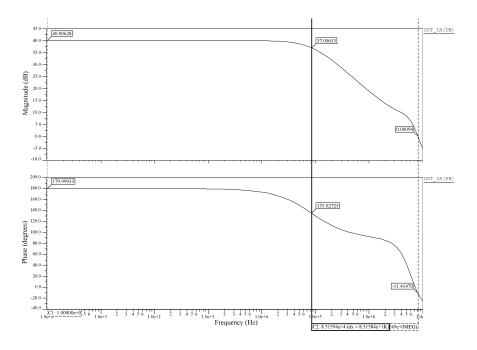

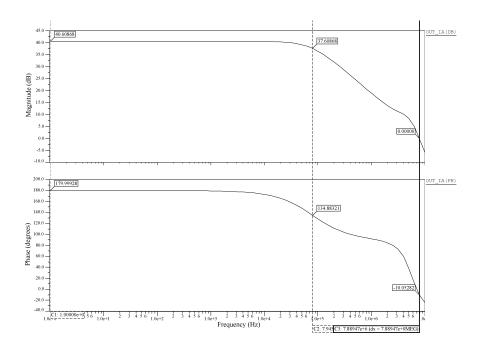

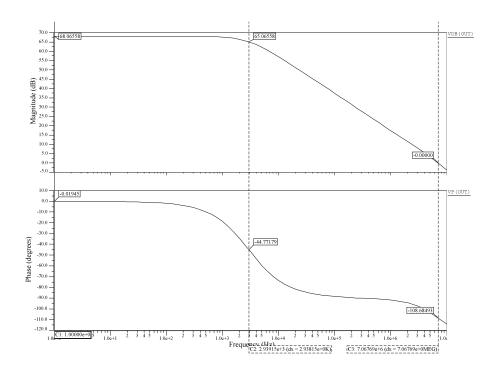

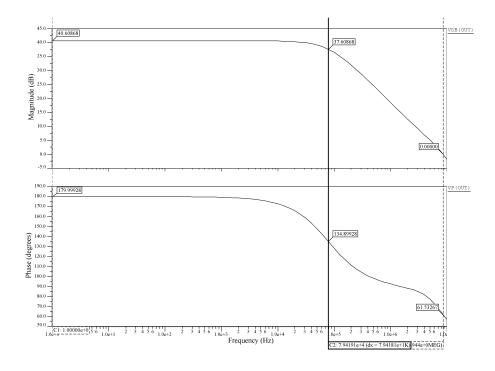

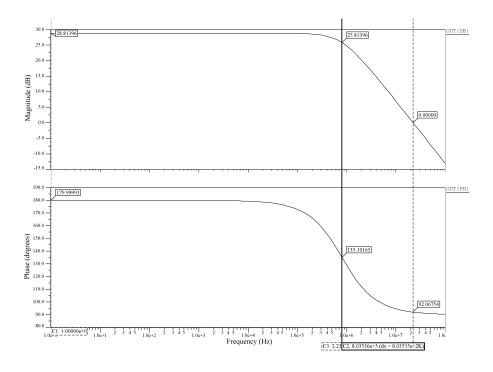

| 5.10 | IA's Frequency response                                                   | 97  |

| 5.11 | Circuit configuration for measuring the voltage transfer curve of the IA. | 98  |

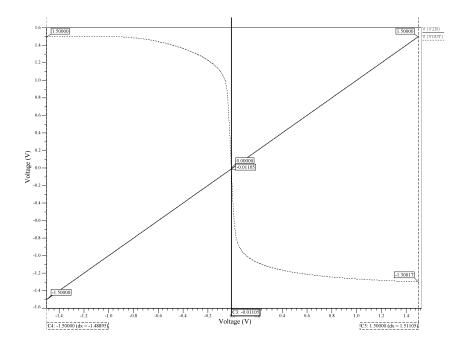

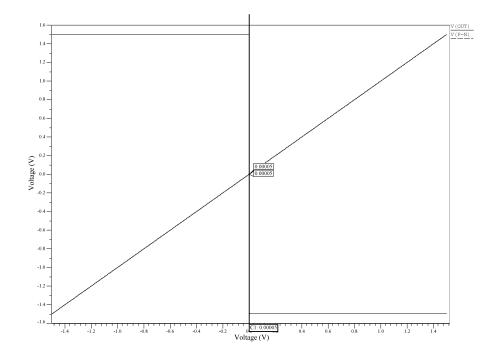

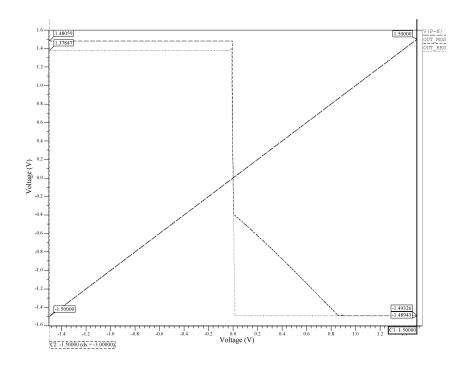

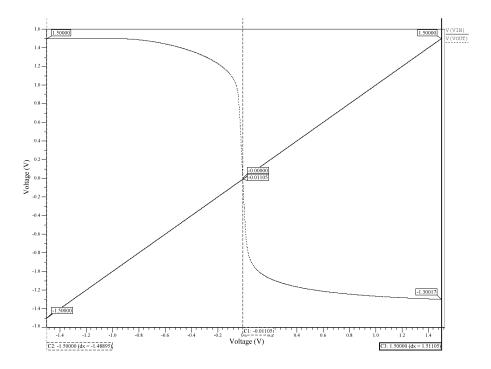

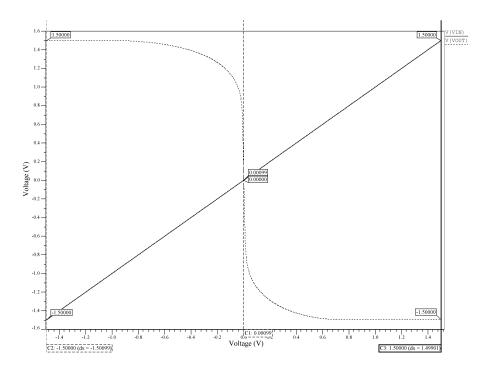

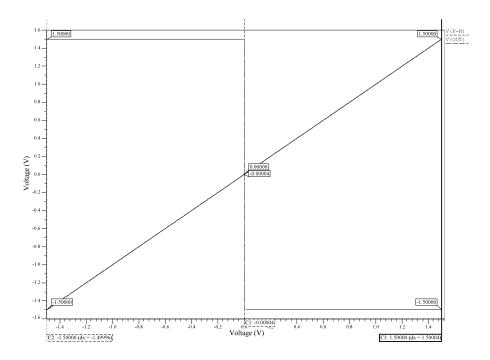

| 5.12 | Voltage transfer curve from circuit of Figure 5.11                        | 99  |

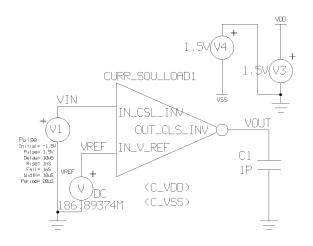

| 5.13 | Circuit configuration for testing the time response of the IA. $\ldots$ . | 100 |

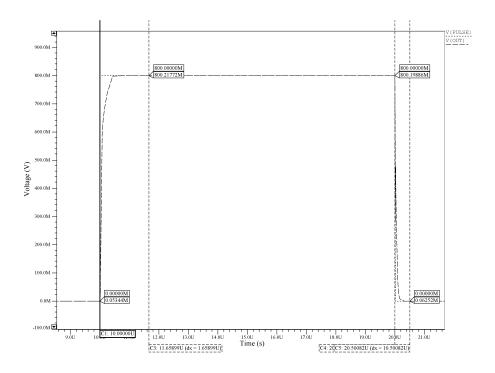

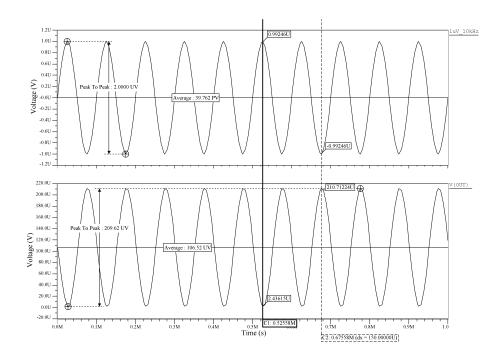

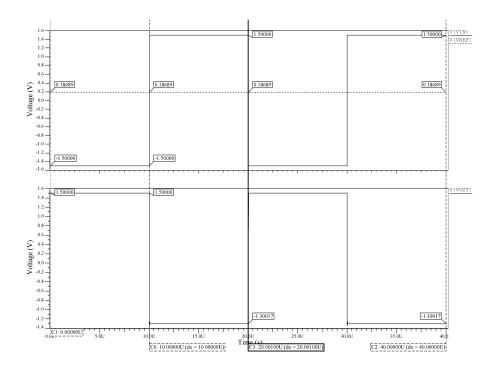

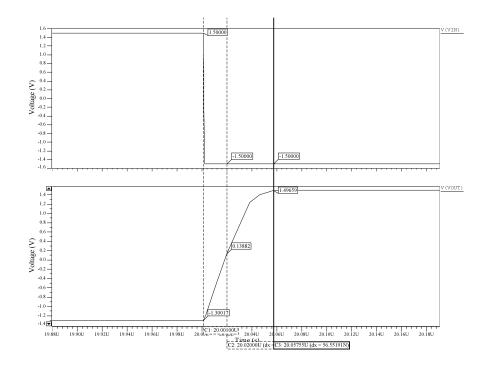

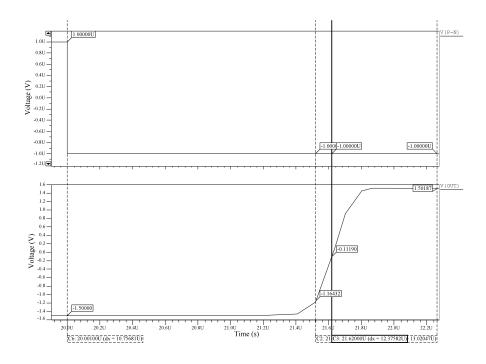

| 5.14 | Time response from circuit of Figure 5.13 at $f = 10 \ kHz$               | 100 |

| 5.15 | Time response from circuit of Figure 5.13 at $f = 100 \ kHz$              | 101 |

| 5.16 | Circuit configuration for testing the frequency response of the current-  |     |

|      | source inverter.                                                          | 102 |

| 5.17 | Frequency response from circuit of Figure 5.17                            | 102 |

| 5.18 | Voltage transfer curve from circuit of Figure 5.16                        | 103 |

| 5.19 | Circuit configuration for testing the time response of the current-source                                                                                                                               |      |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|      | inverter                                                                                                                                                                                                | 104  |

| 5.20 | Current-source inverter time response.                                                                                                                                                                  | 104  |

| 5.21 | Closer view at the output falling edge of the current-source inverter                                                                                                                                   |      |

|      | waveform                                                                                                                                                                                                | 105  |

| 5.22 | Closer view at the output rising edge the current-source inverter waveform                                                                                                                              | .105 |

| 5.23 | Circuit configuration for measuring the voltage transfer curve of each of                                                                                                                               |      |

|      | the push-pull inverter amplifiers                                                                                                                                                                       | 106  |

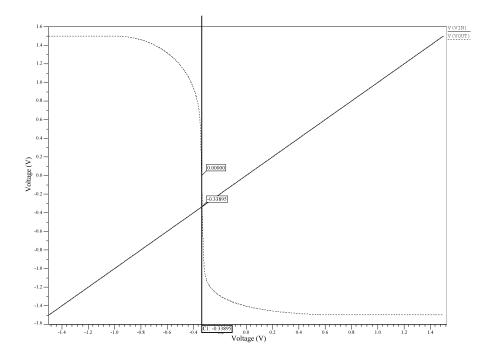

| 5.24 | Voltage transfer curve of inverter A module                                                                                                                                                             | 107  |

| 5.25 | Voltage transfer curve of inverter B module                                                                                                                                                             | 107  |

| 5.26 | Voltage transfer curve of inverter C module. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                               | 108  |

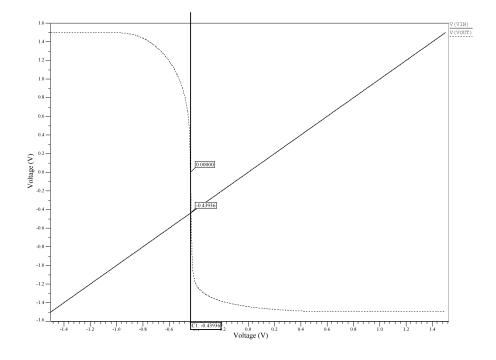

| 5.27 | Voltage transfer curve of the triple push-pull inverter with a load of                                                                                                                                  |      |

|      | $CL = 1 \ pF.$                                                                                                                                                                                          | 109  |

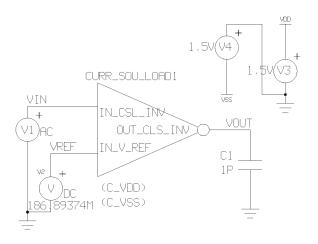

| 5.28 | Circuit configuration for testing the open-loop frequency response of the                                                                                                                               |      |

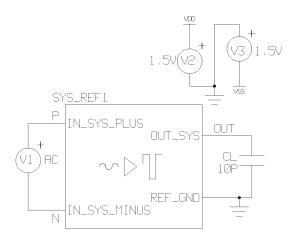

|      | complete system.                                                                                                                                                                                        | 110  |

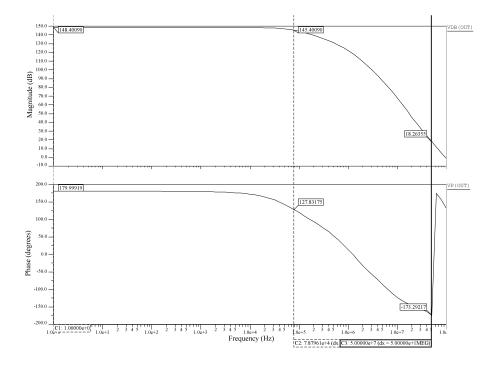

| 5.29 | Frequency response from circuit of Figure 5.28                                                                                                                                                          | 110  |

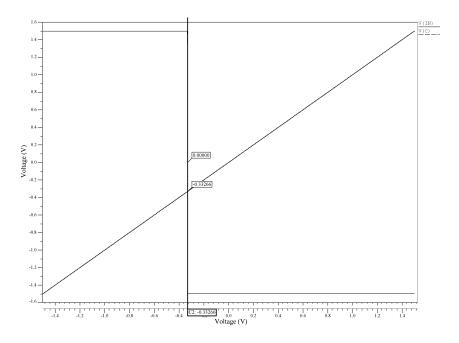

| 5.30 | Voltage transfer curve from circuit Figure 5.28                                                                                                                                                         | 111  |

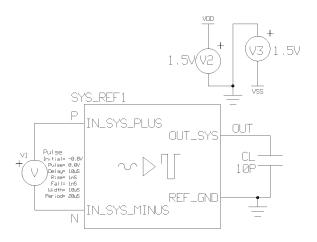

| 5.31 | Circuit configuration for the testing time response of the signal condi-                                                                                                                                |      |

|      | tioning system.                                                                                                                                                                                         | 112  |

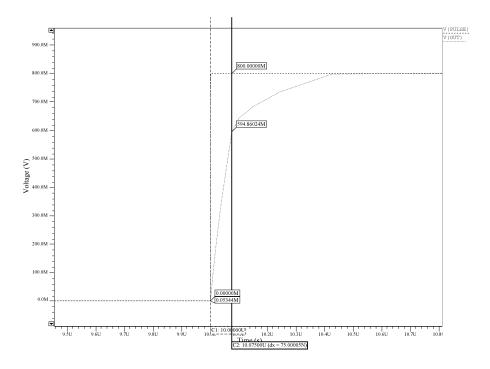

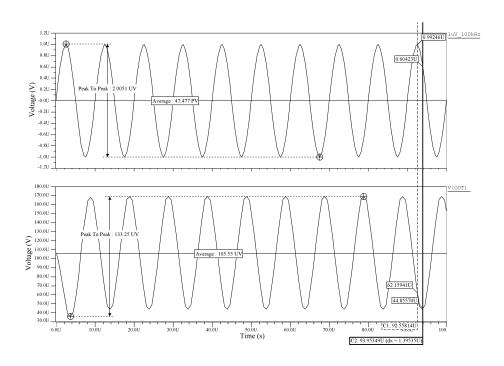

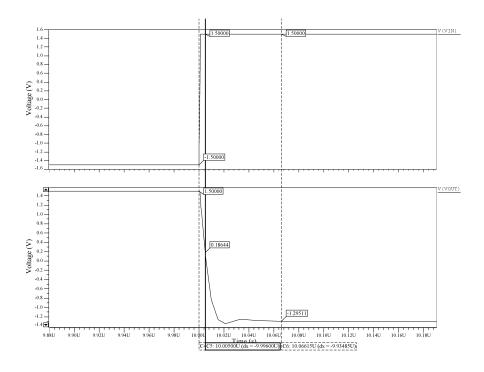

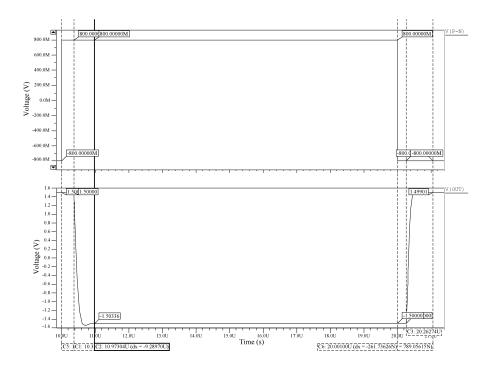

| 5.32 | Time response from circuit of Figure 5.31                                                                                                                                                               | 112  |

| 5.33 | Time response from circuit of Figure 5.31 with an applied input of                                                                                                                                      |      |

|      | $V_{PULSE} = 1 \ \mu V.\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots$ | 113  |

| 5.34 | Closer view at the output rising edge of Figure 5.33                                                                                                                                                    | 114  |

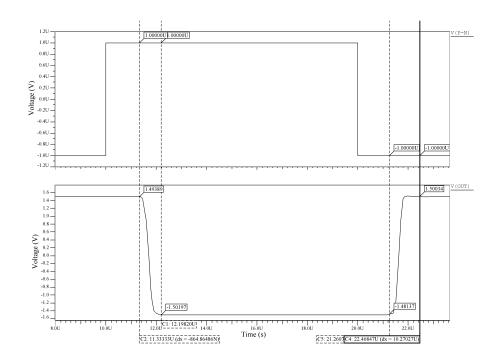

| 5.35 | Transient response from circuit of Figure 5.31 with an applied input of                                                                                                                                 |      |

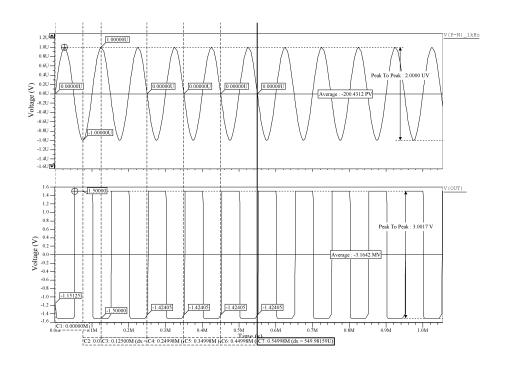

|      | $V_{IN} = 1 \ \mu V$ at 10 $kHz$                                                                                                                                                                        | 115  |

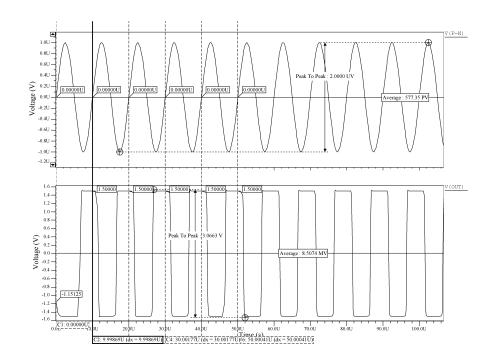

| 5.36 | Transient response from circuit of Figure 5.31 with an applied input of                                                                                                                                 |      |

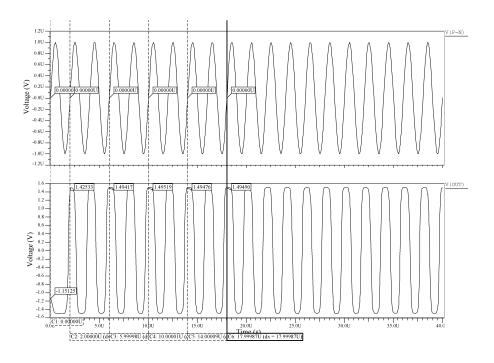

|      | $V_{IN} = 1 \ \mu V$ at 100 kHz.                                                                                                                                                                        | 115  |

| 5.37 |                                                                                                                                                                                                         |      |

|      | $V_{IN} = 1 \ \mu V$ at 500 kHz                                                                                                                                                                         | 116  |

| 6.1  | Layer stack for layout.                                                                                                                                                                                 | 118  |

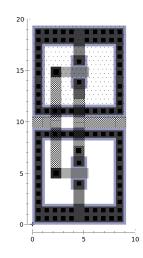

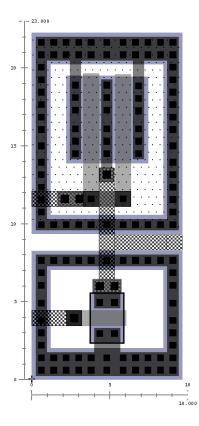

| 6.2  | Layout of the push-pull inverter module A                                                                                                                                                               | 118  |

| 6.3  | Layout of the push-pull inverter module B                                                                                                                                                               | 119  |

| 6.4  | Layout of the push-pull inverter module C                                                                                                                                                               | 119  |

| 6.5  | Layout of the triple inverter module                                        | 120 |

|------|-----------------------------------------------------------------------------|-----|

| 6.6  | Layout of the current-source inverter module                                | 122 |

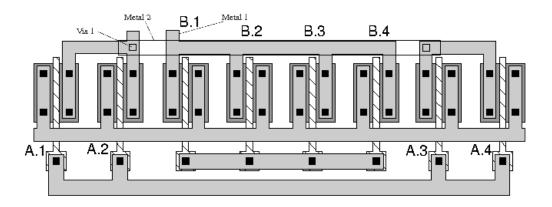

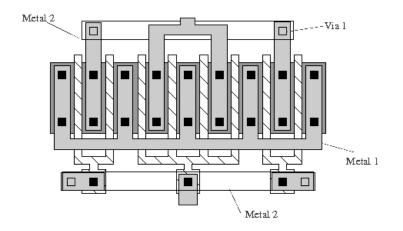

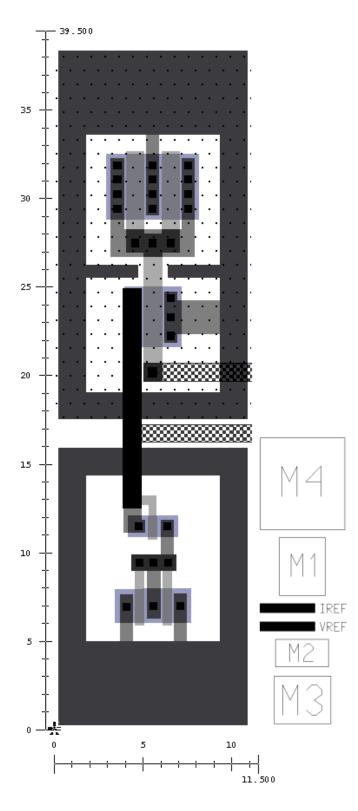

| 6.7  | Layout of the differential pair amplifier module                            | 124 |

| 6.8  | Detailed view of the input transistors of Figure 6.7                        | 125 |

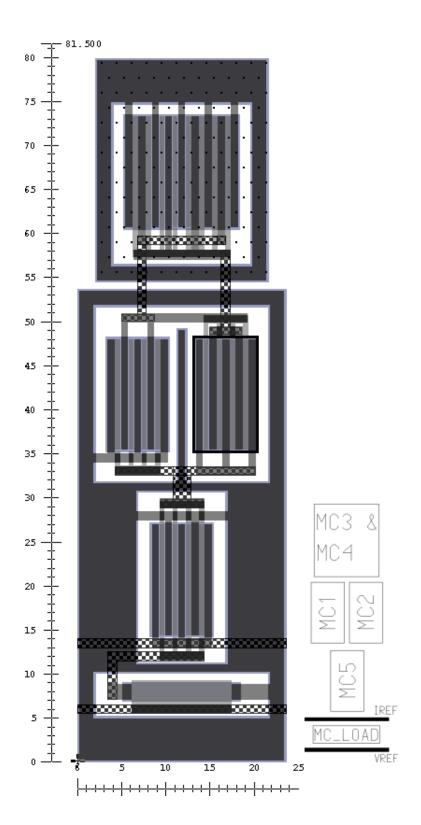

| 6.9  | Layout of the current-source load module                                    | 126 |

| 6.10 | Layout of the bias voltage circuit module.                                  | 127 |

| 6.11 | Layout of the bias current circuit module                                   | 128 |

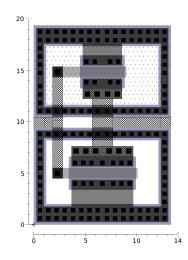

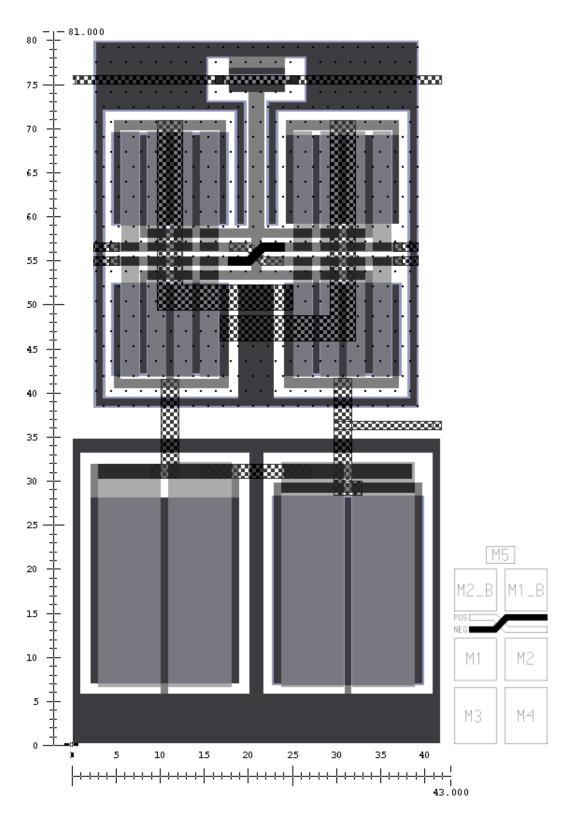

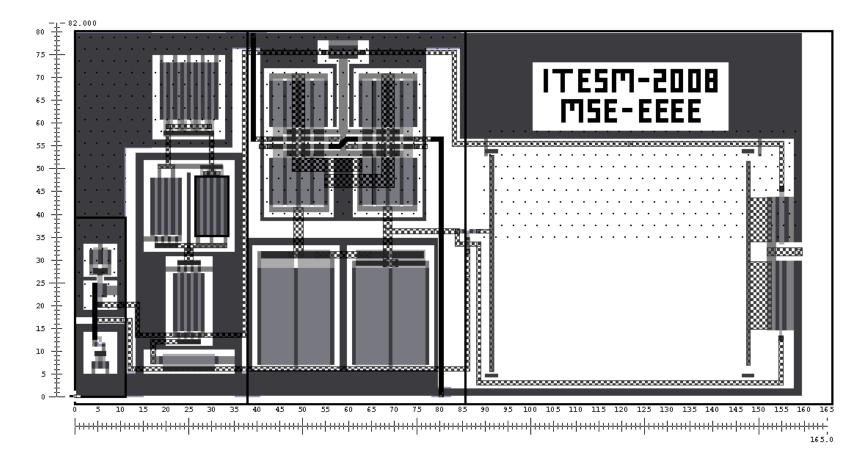

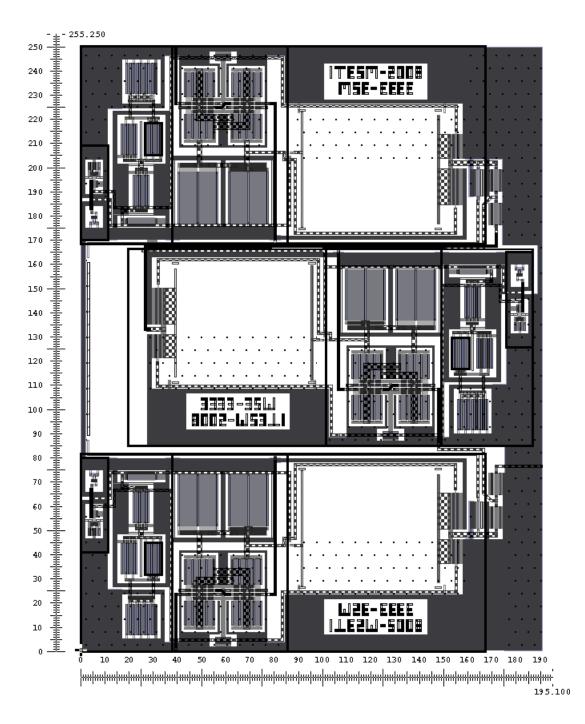

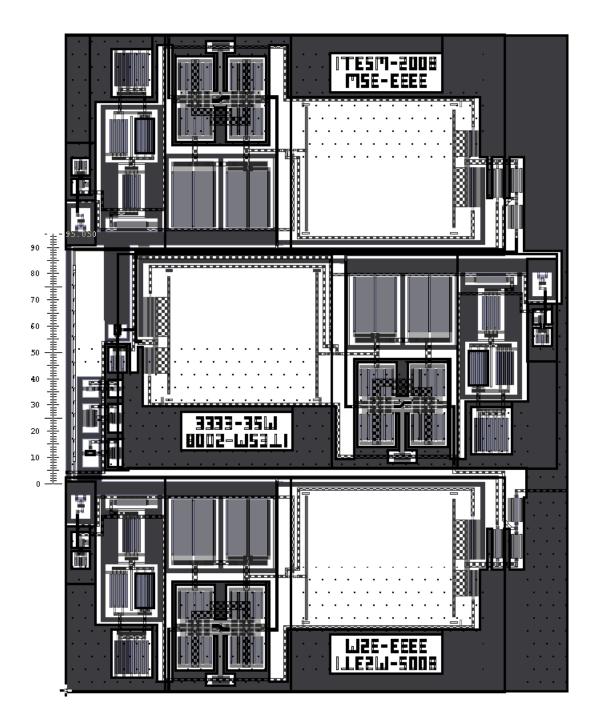

| 6.12 | Layout of the OTA circuit module.                                           | 130 |

| 6.13 | Layout of the OTA circuit module with $VREF$ output terminal                | 131 |

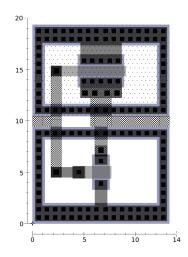

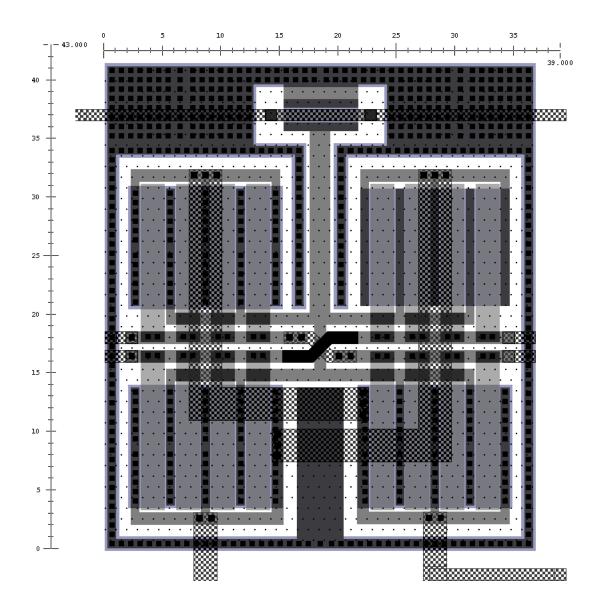

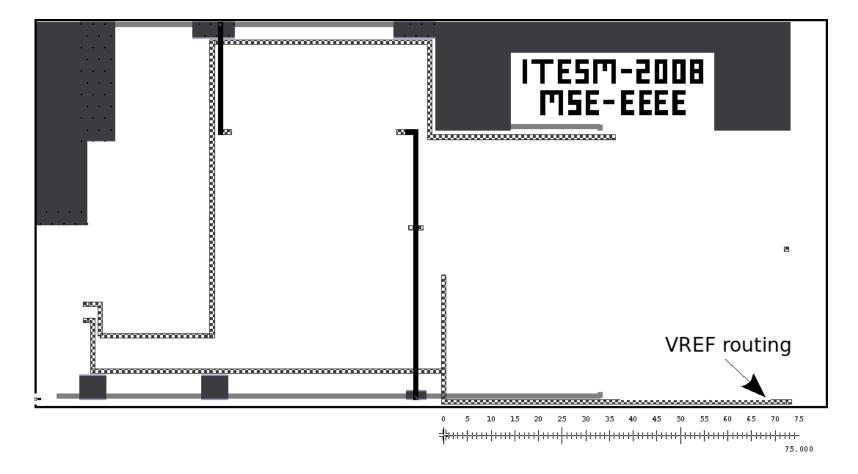

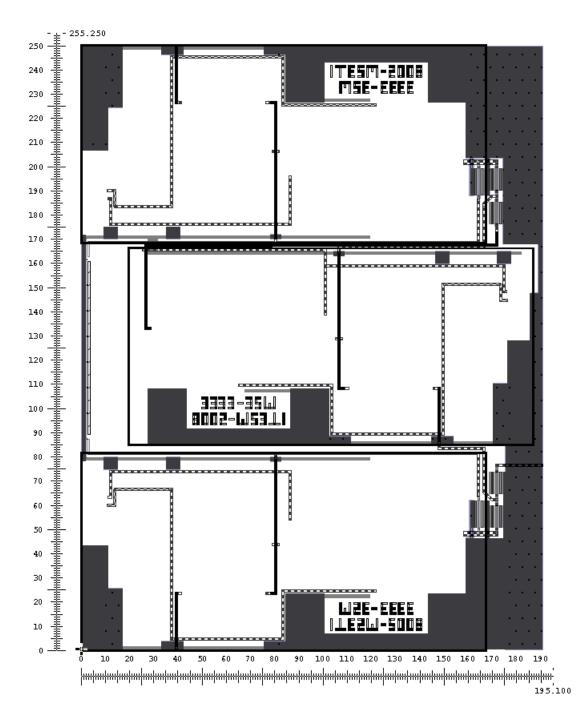

| 6.14 | Layout of the IA circuit module                                             | 133 |

| 6.15 | Simplified layout of the IA circuit module                                  | 134 |

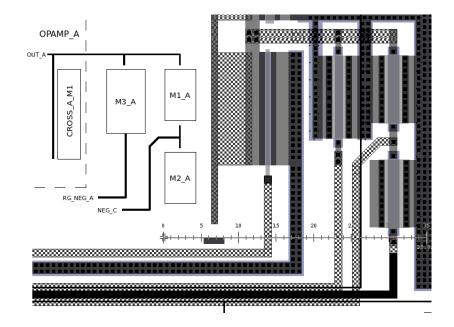

| 6.16 | Closer view of the output mesh from $OPAMP\_A$ configured for the IA        |     |

|      | layout                                                                      | 135 |

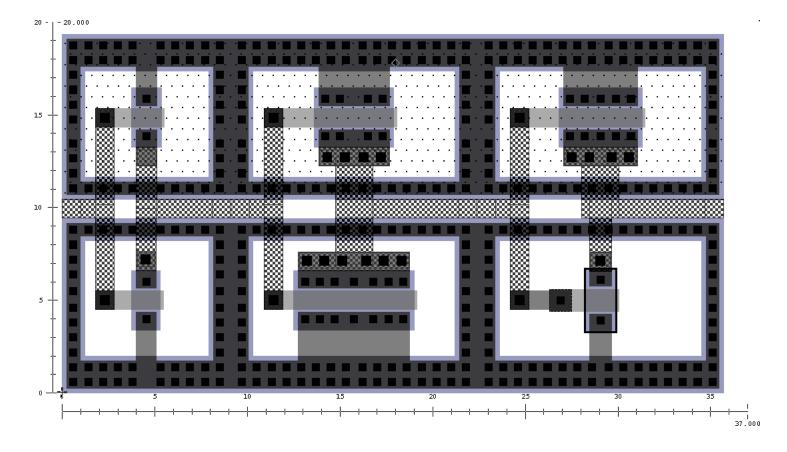

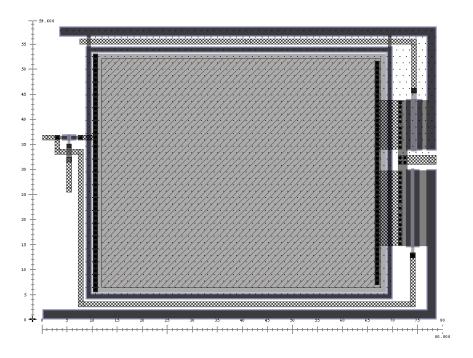

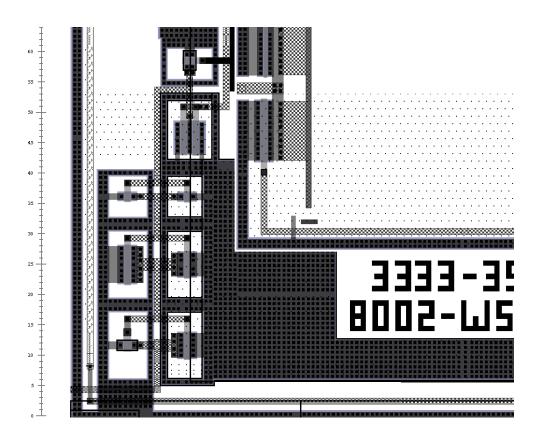

| 6.17 | Layout design of the signal conditioning system                             | 136 |

| 6.18 | Closer view of the inverter modules placement from Figure 6.17              | 137 |

| A.1  | Fragment of the design iterations record by applying $g_m/I_D$ methodology, |     |

|      | part A                                                                      | 140 |

| A.2  | Fragment of the design iterations record by applying $g_m/I_D$ methodology, |     |

|      | part $B$                                                                    | 141 |

# List of Tables

| 2.1  | Dependence of the small-signal model parameters operating in the sat-                                                                       |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | uration region $[2]$                                                                                                                        | 13  |

| 4.1  | OTA design specifications                                                                                                                   | 44  |

| 4.2  | CMOS process parameters [2]                                                                                                                 | 44  |

| 4.3  | Transistor sizes resulted from the first design iteration of OTA $\ . \ . \ .$                                                              | 51  |

| 4.4  | Transistor sizes of the two-stage CMOS OTA circuit with $A_V(dB) \approx$                                                                   |     |

|      | $95.85 \ dB \ldots $ | 55  |

| 4.5  | Transistor sizes of the two-stage CMOS OTA circuit with $A_V(dB)\approx 68~dB$                                                              | 55  |

| 4.6  | Transistor sizes of the bias voltage circuit                                                                                                | 60  |

| 4.7  | Transistor sizes of the bias current circuit                                                                                                | 65  |

| 4.8  | Transistor sizes of the modified differential pair circuit $\ldots \ldots \ldots$                                                           | 67  |

| 4.9  | Resistance values from the IA circuit.                                                                                                      | 74  |

| 4.10 | Transistor parameters for replacing resistances from circuit Figure 4.23                                                                    | 78  |

| 4.11 | Transistor sizes of current-source inverter circuit module                                                                                  | 82  |

| 4.12 | Transistor sizes of the three push-pull inverter circuit modules $\ldots$ .                                                                 | 85  |

| 5.1  | DC operating point voltage of the bias voltage module at different loads                                                                    | 90  |

| 5.2  | DC operating point voltage of the bias current module at different loads                                                                    | 91  |

| 6.1  | OTA modules layout area                                                                                                                     | 135 |

| 6.2  | Inverter modules layout area                                                                                                                | 137 |

# Chapter 1

# Introduction

Recent advances in complementary metal-oxide semiconductor (CMOS) processing and micromachining technologies have allowed various types of microsensors to be integrated within signal processing circuit in a single chip. The so-called *systems on chip* are increasingly used in many biomedical and chemical applications [9].

The use of microelectromechanical systems (MEMS) as sensors and microestructures offers several advantages, such as excellent mechanical properties, mature integrated circuit (IC) technology and low cost fabrication. Moreover, some emerging applications include gyroscopes, microphones, spectrometers, liquid chromatographs, bio-labs on a chip (chemical, biological and nanochemical) [10]. These systems on chip are capable of measure: tactile pressure [11], barometric pressure [12], acceleration [13], pH level [14], electrochemical concentrations [15] and ultrasonic signals [7], among other physical parameters. The magnitude of the electronic signal obtained from MEMS sensors can be of the order of 5  $\mu V$ . Depending on the sensing mechanism and the signal nature as well, it could be either ac-current, dc-current, ac-voltage, or dc-voltage [14]. Therefore, on each MEMS application, there is a need for a low-power interface circuit, which serves as a bridge between the on-chip sensor and the back-end digital processor [16].

### 1.1 Problem Statement

The BioMEMS Research Group at Instituto Tecnológico y de Estudios Superiores de Monterrey, Campus Monterrey is developing a MEMS fully functional biosensor to monitor leukemia patients after treatment [17, 18]. The sensor mechanism is based on the resonant behavior of silicon cantilever beams. The advantage of resonant sensors is that the frequency output is already in digital form, and hence, can be more safely transmitted from the transducer element to an electronic circuit [19]. However, the small variation generated by the sensing mechanism produces very small changes in the electronic signal [20].

Moreover, the BioMEMS Research Group is developing a multiplexed potentiostat system to convert the ionic current produced by an electrolytic reaction to a measurable signal. In order to comply with this application, a low-noise, good linearity and high sensitivity amplifier is required for developing the potentiostat microelectronic circuit [21].

This thesis develops a CMOS analog signal conditioning circuit for a low-voltage differential signal coming from resonant microsensors. The thesis defines a proper configuration for the microelectronic circuit as well as its physical layout. The process technology used is the 2-poly, 4-metal, 0.35  $\mu m$  CMOS from Austriamicrosystems® (AMS) and the circuit is designed to operate at 3 V rail to rail. The design should be capable of amplifying signals of the order of 1  $\mu V$  and hundreds of kHz as well.

## 1.2 Objectives

The general objective of this thesis is to design a CMOS circuit capable of reading and amplifying a low-voltage differential signal from a resonant sensor. The circuit will overcome noise sources in order to provide measurable signals to standard microelectronic circuits [22]. The complete system will be implemented in layout form, complying with general analog matching techniques [23], for its later integration to the projects currently in development by the BioMEMS Research Group. The specific objectives are:

- To design a CMOS signal conditioning circuit for sensing resonant beams, following a well specified methodology.

- To design the schematic diagram of the circuit by implementing the 0.35  $\mu m$  process technology from AMS®.

- To design the layout of the circuit, taking advantage of general matching layout techniques for a robust physical design.

• To complete both, a functional microelectronic circuit design and a well established layout design for a two-stage CMOS operational transconductance amplifier (OTA), in order to apply this design on the signal conditioning system in the current projects of the BioMEMS Research Group.

The key contributions of this thesis are the design methodology of the CMOS circuit which can be adapted to the requirements of a specific project, and the layout design of the schematic circuit diagram, considering general matching techniques while achieving proper performance.

### **1.3** Previous Work

The merging of silicon microfabrication techniques with surface functionalization biochemistry offers new exciting opportunities in developing microscopic biomedical analysis devices with unique characteristics. Micromechanical transducers for chemical and biosensing applications represent one possibility.

Several biomedical applications can be foreseen, such as monitoring presence and concentration of substances in a solution or gas, calculating specific *binding energies*<sup>1</sup>, monitoring chemical surface reactions, studying adsorption-desorption processes of substances (isotherms and kinetics). This can in principle be done from the single molecule scale up to the whole cell behavior [5].

Yazdi *et al.* [24] presented a review of a variety of capacitive front-end circuits for high-precision accelerometers. The capacitance readout schemes were compared based on their readout resolution. Also, a high-performance switched-capacitor readout frontend for  $\mu g$  accelerometers with high direct current (dc) stability is described. The circuit was implemented in 0.5  $\mu m$ , 5 V CMOS process technology and used correlated double sampling (CDS) for amplifier finite gain, 1/f noise, offset cancellation, and chopperstabilization of the switches to improve matching to further reduce the offset. The final result was a hybrid-package interface circuit with a sensitivity of 430 mV/g and a resolution of 1.6  $\mu g/\sqrt{Hz}$  at ambient pressure.

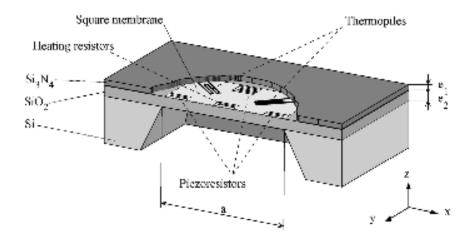

Rufer *et al.* [7] described the design of a silicon membrane thermally actuated at its resonant frequency of 40 kHz. The membrane had a piezoresistive bridge for monitoring deflections. The electronics of the measurement stage was developed in a

$<sup>^{1}</sup>Binding \ energy$  is the mechanical energy required to disassemble a whole into separate parts.

0.8  $\mu m$  CMOS technology. The voltage output of a Wheatstone bridge was amplified by two differentiators and a differential amplifier. The maximum peak-to-peak voltage at the output of the Wheatstone bridge was about 20  $\mu V$ . Each differentiator gave a voltage gain of around 12 at the frequency band centered at 40 kHz while the gain of the differential amplifier was 100. The device showed 35 mV/Pa of sensitivity.

Zhang *et al.* [25] designed a *reconfigurable* transducer interface circuit whose supply voltage is 3.3 V. The device was developed with a 3-metal, 2-polysilicon, 0.5  $\mu m$ CMOS process technology. The digital control circuit, memory, and I/O ports was described in Verilog and the modules were synthesized using the Cadence B Buildgates synthesis tool. Physical design of the analog front-end was carefully considered to maximize performance. For instance, common centroid layout techniques were used to reduce the input offsets and match passive component values. The total chip area was  $2.2 \ mm \ \times \ 2.2 \ mm$  and it dissipated 53  $\mu W$  in a typical four-sensor application. The interface chip could achieve sensitivities of 30 mV/fF and 18  $mV/\Omega$ .

Chiou *et al.* [26] developed a vertical comb drive resonator with piezoresistance sensor. The structure was fabricated through a standard 2-poly, 4-metal, 0.35  $\mu m$ process and its frequency ranged from 5 kHz to 20 kHz. The first resonance frequency was approximately 14.5 kHz. The resonant frequencies and the corresponding mode shapes were calculated by using a Finite-Element Mode (FEM) simulator. The sensing piezoresistor showed variations in the order of hundreds of ohms, thus a variation of just a few  $\mu V$  was obtained from the sensor. Since the resonator will be used for measuring environmental humidity and virus detection, a need for a signal conditioning circuit to monitor the physical variations was discussed.

Thanachayanont and Sangtong [27] proposed a current-mode Wheatstone bridge for low-voltage current-sensing configuration, named as AZKA cell. This configuration presents several advantages over traditional Wheatstone bridge configurations, such as a simple linearization technique and reduction of resistive sensing elements. Some drawbacks of the AZKA cell were the vital matching of current mirror transistor pairs. The circuit was designed to operate with a single 1.5 V power supply and uses a  $0.35 \ \mu m$  process technology. The complete interface circuit proposed was targeted for an implantable pressure sensor with a sensitivity of  $5 \ \mu V/V/mmHg$ .

Narula *et al.* [15] presented the design of a potentiostat interface circuit capable to measure currents generated in reduction and oxidation (redox) reactions. These ionic currents ranged from 1 pA to 200 nA in the electrochemical cell.

Bracke *et al.* [28] illustrated a new generic architecture for an ultra low power capacitance to voltage converter with very low power consumption (less than 100  $\mu W$ ). The design consisted on a fully differential class AB OTA with folded cascode stage and switched capacitor (SC) common mode feedback and a CDS scheme to eliminate the effect of the offset on the sensor interface. The input transistors of the AB OTAs were biased in weak inversion to reduce the power consumption. The total current consumption of this amplifier was 4  $\mu A$ . Moreover, the paper shows an interesting noise analysis for the AB OTAs and the SC devices.

### 1.4 Thesis Outline

This thesis work is organized in seven chapters that are described as follows. Chapter 1 presents a descriptive overview of the problem, general and specific objectives, and a literature review of important work performed in this area.

Chapter 2 states the theoretical framework or background of CMOS analog integrated circuit design, focusing on the key concepts required for the understanding of the individual system stages operation. Moreover, the chapter includes the fundamental layout design concepts for analog circuit design.

Chapter 3 gives an overview on mechanical microsensors technology, in order to offer a comprehensive introduction to the basic design of MEMS.

Chapter 4 defines the minimal requirements of the signal conditioning system, and a step-by-step design methodology applied to obtain the electronic schematic circuit diagram of each stage. A modular methodology is implemented on the CMOS circuit design. Once defined all stages of the complete system, they are integrated and the final schematic circuit diagram is obtained.

Chapter 5 introduces the results from the simulation analysis of the individual circuit modules designed and the integrated signal conditioning system, as well as an evaluation and discussion of results.

Chapter 6 introduces the layout concepts applied to the schematic circuit diagram. At the end, the complete theoretical system will developed in layout format.

Chapter 7 contains the conclusions of the thesis and discusses future work.

# Chapter 2

# **Principles of Analog Circuit Design**

## 2.1 Introduction

The design of analog circuits relies on an understanding of the transistor models used. For hand calculations, only first-order models are used to evaluate circuit performance. However, many small details of circuit behavior, such as precise gain, distortion, and noise, depend on second-order transistor characteristics. Therefore, second-order characteristics must be included in the circuit verification. A full model will always be used to verify the circuit performance by means of a circuit simulator, such as Mentor Graphics  $ICstudio(\mathbb{R})$ . We cannot learn circuit behavior by just running ICstudio( $\mathbb{R}$ ). The best insight is obtained primarily by performing simple hand calculations. Thus, simple models must be used for qualitative results. ICstudio( $\mathbb{R}$ ) can then be used to verify the assumptions made and to validate the circuit performance [22].

This chapter, reviews the principles of analog circuit design. The chapter starts with a description of the fabrication and operation of the MOS transistor. Thenafter, two additional sections defines the basic configurations of CMOS analog circuits. Finally, the last section presents the general techniques applied to design the IC layout.

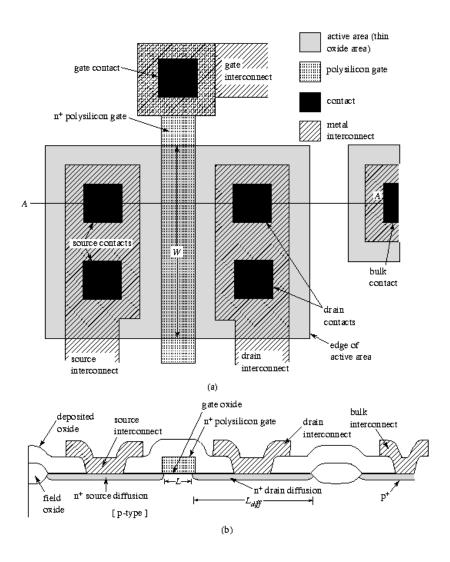

### 2.2 The MOS Transistor

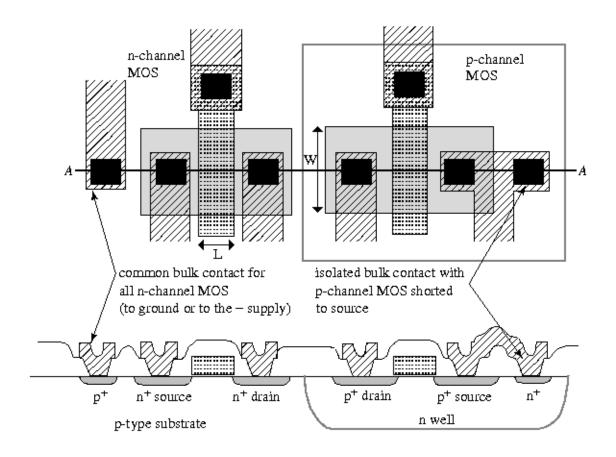

Figure 2.1 shows the structure of an n-channel and p-channel MOS transistor using an n-well technology. The p-channel device is formed with two heavily doped  $p^+$  regions diffused into a highly doped  $n^-$  material called the *well*. The two  $p^+$  regions are called drain and source and are separated by a distance L (referred to as device length). At the surface between the drain and source lies a gate electrode that is separated from the silicon by a thin dielectric material (silicon dioxide). Similarly, the n-channel transistor is formed by two heavily doped  $n^+$  regions within a lightly doped  $p^-$  substrate. This transistor also has a gate on the surface between the drain and source separated from the silicon by a thin dielectric material (silicon dioxide). Essentially, both transistors are four terminal devices as shown in Figure 2.1. For an *n-well process*, the p-bulk connection is common throughout the integrated circuit and is connected to  $V_{SS}$  (the most negative supply). Multiple n-wells can be fabricated on a single circuit, and they can be connected to different voltages, in various ways depending upon the application [2].

Figure 2.1: Physical structure of MOS transistors.

#### 2.2.1 Operating Regions

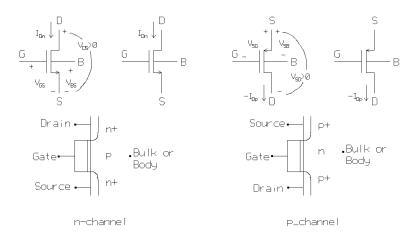

The Figure 2.2 shows both, the symbol of an n-channel MOS transistor and the symbol of a p-channel MOS transistor, illustrating their four terminals: gate, source, drain and bulk. In the case of the n-channel MOS transistor, when it operates as a switch, the transistor "connects" the source and the drain together if the gate voltage,  $V_G$ , is high and isolates the source and the drain if  $V_G$  is "low" [1].

Figure 2.2: The MOS transistor symbol.

Consider a n-channel MOS transistor connected to external voltages. As  $V_G$  becomes more positive, the holes in the p-substrate are repelled from the gate area, leaving negative ions behind so as to mirror the charge on the gate. In other words, a *depletion region* is created. Under this condition, no current flows because no charge carriers are available. As  $V_G$  increases, so do the width of the depletion region and the potential at the oxide-silicon interface. When the the interface potential reaches a sufficiently positive value, electrons flow from the source to the interface and eventually to the drain. Thus, a *channel* of charge carriers is formed under the gate oxide between source and drain and the transistor is "turned on". At this moment, the interface region is *inverted* [1].

If  $V_G$  rises further, the charge in the depletion region remains relatively constant while the channel charge density continues to increase, providing a greater current,  $I_D$ , from source to drain. This means that the larger the value of the gate potential, the more the electrons and the "heavier" the inversion is at that point. A few volts of variation of the gate potential can vary the population of electrons there by several orders of magnitude. Although such variation is continuous, we often say that as the gate potential is raised, transistor goes from *weak* inversion to *moderate* inversion, and eventually to *strong* inversion. This division into three regions is very convenient, because distinct behaviors are observed in each of the three regions [29].

As  $V_{GS}$  or  $V_{DS}$  is reduced, the current in the channel can eventually become so small that it is masked by the leakage current of the reverse-biased drain-body junction (or even the leakage from the inversion layer to the substrate). In weak inversion region, the current turns out to be due to the diffusion of carriers and  $I_D$  is, for all practical purposes, exponentially related to  $V_{GS}$ .

In strong inversion, the current turns out to be due to drift. In the *saturation* part of strong inversion,  $I_D$  is found to be approximately quadratic in  $V_{GS}$  for long-channel devices.

In moderate inversion, both drift and diffusion currents contribute significantly. In this region,  $I_D$  is neither exponential nor polynomial; rather its behavior changes gradually from one form of functional dependence to the other, as  $V_{GS}$  is raised by a few tenths of a volt. Within this region, the current can vary by a couple of orders of magnitude [29].

#### 2.2.2 Large-Signal Model

As demonstrated in [29], when the length and width of the MOS device is greater than about 10  $\mu m$ , the substrate doping is low, and when a simple model is desired, the model suggested by Sah [30] is very appropriate. The model equation for an n-channel MOS transistor is developed in Eq. (2.1) as follows

$$I_D = \frac{\mu_0 C_{OX} W}{L} \left[ (V_{GS} - V_T) - \frac{V_{DS}}{2} \right] V_{DS}$$

(2.1)

Where  $\mu_0$  is the surface mobility of the channel,  $C_{OX}$  is the capacitance per unit area of the gate oxide, W is the effective channel width and L is the effective channel length. This same model can be used for the p-channel MOS device if all voltages and currents are multiplied by -1 and the absolute value of the p-channel threshold is used.

In order to express the model equations in terms of electrical parameters, there is defined the *transconductance parameter*, K' is defined as follows

$$K' = \mu_0 C_{OX} \tag{2.2}$$

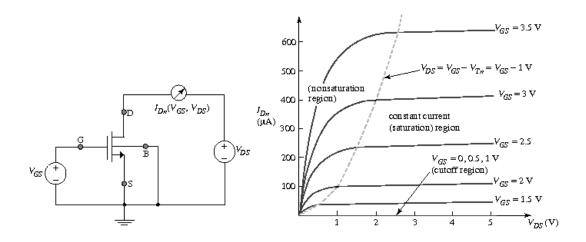

Based on the model of Eq. (2.1) there are three regions of operation for the MOS transistor. These regions depend on the value of  $V_{GS} - V_T$ . If  $V_{GS} - V_T$  is zero or negative, then the MOS device is in the *cut-off*<sup>1</sup> region see Figure 2.3 and Eq. (2.1) becomes

$$I_D = 0, \qquad V_{GS} - V_T \le 0$$

(2.3)

In this region, the channel acts like an open circuit.

Figure 2.3: Polarization circuit and  $I_D$  response of an n-channel MOS transistor.

If  $V_{DS}$  is less than  $V_{GS} - V_T = V_{DS}(sat)$ , then the MOS transistor is in the *nonsaturation* region (see Figure 2.3) and Eq. (2.1) becomes

$$I_D = K' \frac{W}{L} \left[ (V_{GS} - V_T) - \frac{V_{DS}}{2} \right] V_{DS}, \qquad 0 < V_{DS} \le (V_{GS} - V_T)$$

(2.4)

The transistor enters in saturation see Figure 2.3 when  $V_{DS}$  is greater than  $V_{DS}(sat)$  or  $V_{GS} - V_T$ . At this point the current  $I_D$  becomes independent of  $V_{DS}$ . Therefore, replacing  $V_{DS}$  by  $V_{DS}(sat)$  of Eq. (2.1), the result is [2]

$$I_D = K' \frac{W}{2L} (V_{GS} - V_T)^2, \qquad 0 < (V_{GS} - V_T) \le V_{DS}$$

(2.5)

Since the MOS transistor is a bidirectional device, determining which physical node is the drain and which the source may seem arbitrary. However, for an n-channel transistor, the source is always connected to the lower potential of the two nodes, and for the p-channel transistor, the source is always at the higher potential. It is

<sup>&</sup>lt;sup>1</sup>MOS transistors can operate in the subthreshold region [22, 29].

obvious that the drain and source designations are not constrained to a given node of a transistor, but can switch back and forth depending on the terminal voltages applied to the transistor.

The large-signal model is used to solve for the drain current given the terminal voltages of the MOS device [2]. Equations (2.4) and (2.5) serve as the foundation for analog CMOS design, describing the dependence of  $I_D$  upon the constant of the technology,  $\mu_n C_{OX}$  [referenced in Eq. (2.2) above], the device dimensions, W and L, and the gate and drain potentials with respect to the source [1].

#### 2.2.3 Linear Characteristics

If in Eq. (2.4),  $V_{DS} \ll 2(V_{GS} - V_T)$ , we have

$$I_D \approx K' \frac{W}{L} (V_{GS} - V_T) V_{DS}$$

(2.6)

That is, the drain current is a *linear* function of  $V_{DS}$ . This is also evident from the characteristics of Figure 2.3 for small  $V_{DS}$ . As shown in Figure 2.4, each parabola can be approximated by a straight line. The linear relationship implies that the path from the source to the drain can be represented by a linear resistor equal to

$$R_{on} = \frac{1}{K' \frac{W}{L} (V_{GS} - V_T)}$$

(2.7)

A MOS transistor can therefore operate as a resistor whose value is controlled by the overdrive voltage [so long as  $V_{DS} \ll 2(V_{GS} - V_T)$ ]. Note that in contrast to bipolar transistors, a MOS device may be on even if it carries no current. With the condition  $V_{DS} \ll 2(V_{GS} - V_T)$  we say the device operates in deep triode region [1] or ohmic region [29].

### 2.2.4 Small-Signal Model

The small-signal model is a linear model that helps to simplify calculations. It is only valid over voltage or current regions where the large-signal voltage and currents can adequately be represented by a straight line. Figure 2.5 shows a linearized small signal model for the MOS transistor.

Figure 2.4: Linear operation in deep triode region [1].

Figure 2.5: Small-signal model of the MOS transistor.

The various parameters of this small-signal model are all related to the large-signal model parameters and dc variables. The channel conductances  $g_m$ ,  $g_{mbs}$  and  $g_{ds}$  are defined as (evaluated at the quiescent point) [2]

$$g_m = \frac{\partial i_D}{\partial v_{GS}} \tag{2.8}$$

$$g_{mbs} = \frac{\partial i_D}{\partial v_{BS}} \tag{2.9}$$

$$g_{ds} = \frac{\partial i_D}{\partial v_{DS}} \tag{2.10}$$

The important dependence of the small-signal parameters on the large-signal model parameters and dc voltages and currents is illustrated in Table 2.1, where  $\phi_F$  is the strong inversion surface potential (Fermi potential, measured in V),  $\gamma$  is the bulk threshold parameter ( $\gamma_N = 0.4 V^{1/2}$  for an n-channel device, and  $\gamma_N = 0.57 V^{1/2}$  for a p-channel device), and  $\beta$  is the transconductance parameter (given in terms of physical

| Small-signal     |                           | dc current and                                                 |                                                                             |

|------------------|---------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------|

| model parameters | dc current                | voltage                                                        | dc voltage                                                                  |

| $g_m$            | $\cong (2K'I_DW/L)^{1/2}$ | _                                                              | $\cong \frac{K'W}{L}(V_{GS} - V_T)$                                         |

| $g_{mbs}$        | _                         | $\frac{\gamma (2I_D\beta)^{1/2}}{2(2 \phi_F + V_{SB} )^{1/2}}$ | $\frac{\gamma [\beta (V_{GS} - V_T)]^{1/2}}{2(2 \phi_F  +  V_{SB} )^{1/2}}$ |

| $_{\_}$ $g_{ds}$ | $\cong \lambda I_D$       | _                                                              | _                                                                           |

Table 2.1: Dependence of the small-signal model parameters operating in the saturation region [2]

parameters as

$$\beta = K' \frac{W}{L} \qquad (A/V^2) \tag{2.11}$$

The small-signal model for the saturation region will be key element in analyzing circuits in the following chapters.

Moreover, an extremely important assumption for the small signal model parameters is [2]

$$g_m \approx 10 \ g_{mbs} \approx 100 \ g_{ds} \tag{2.12}$$

Which is very helpful on simplifying numerical calculations.

### 2.3 Single Stage Amplifiers

Signal amplification is essential in most electronic instrumentation circuits. An analog or digital signal may be too small to drive a load, may require to overcome the noise of a subsequent stage, or may need to match logical levels for a digital input circuit [1]. The inverter is the basic amplifier stage for CMOS circuits. Typically, the inverter uses the common-source configuration with either, an active resistor or a current sink/source [2].

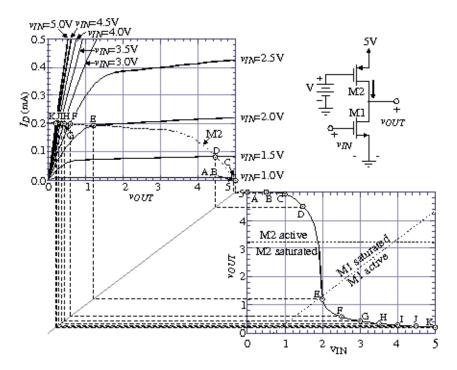

#### 2.3.1 Current-Source Inverter

A current-source inverter amplifier and its voltage transfer curve (VTC) is shown in Figure 2.6. This configuration uses a p-channel MOS transistor as the current-source load. The current source is a common-gate configuration with the gate connected to a dc bias voltage,  $V_{GG2}$ . The regions of operation for the transistors of Figure 2.6 are found by expressing the saturation relationship for each transistor. For M1, this relationship is

$$V_{DS1} \ge V_{GS1} - V_{TN} \to V_{OUT} \ge V_{IN} - V_{TN}$$

$$(2.13)$$

The equivalent relationship for M2 requires careful attention to signs. This relationship is

$$V_{SD2} \ge V_{SG2} - |V_{TP}| \to V_{DD} - V_{OUT} \ge V_{DD} - V_{GG2} - |V_{TP}|$$

(2.14)

The maximum output voltage,  $V_{OUT}(max)$ , of the large-signal output voltage swing for the current-source load inverter is  $V_{DD}$  since when M1 is off. The voltage across M2 can go to zero, allowing the output voltage to be  $V_{DD}$ . Thus, the maximum positive output voltage is

$$V_{OUT}(max) \cong V_{DD} \tag{2.15}$$

The lower limit can be found by assuming that M1 will be in the nonsaturation region.  $V_{OUT}(min)$  can be given as

$$V_{OUT}(min) = (V_{DD} - V_{T1}) \left\{ 1 - \left[ 1 - \left( \frac{\beta_2}{\beta_1} \right) \left( \frac{V_{SG2} - |V_{T2}|}{V_{DD} - V_{T1}} \right)^2 \right]^{1/2} \right\}$$

(2.16)

The result assumes that  $V_{IN}$  is taken to  $V_{DD}$ . The small-signal output resistance of the CMOS inverter with a current-source load can be found as [2]

$$R_{OUT} = \frac{1}{g_{ds1} + g_{ds2}} \cong \frac{1}{I_D(\lambda_1 + \lambda_2)}$$

(2.17)

Where  $\lambda$  id defined as the channel length modulation parameter, with typical values (for a channel length of  $L = 1 \ \mu m$ ) of  $\lambda_N = 0.04 \ V^{-1}$  and  $\lambda_P = 0.05 \ V^{-1}$  for n-channel device and p-channel device, respectively [2].

Figure 2.6: Voltage transfer curve and circuit of the current-source inverter [2].

### 2.3.2 Push-pull Inverter

In comparing the large-signal VTC characteristics between the current-source and the push-pull inverters, a higher gain is obtained by the push-pull inverter assuming identical transistors. This is due to the fact that both transistors are being driven by  $V_{IN}$ . Moreover, the push-pull inverter is capable of a rail-to-rail operation and the VTC transition is usually very sharp [2], [31].

The regions of operation for the push-pull inverter are shown on the VTC of Figure 2.7. These regions are easily found using the definition of  $V_{DS}(sat)$  given for the MOS transistor. M1 is in the saturation region when

$$V_{DS1} \ge V_{GS1} - V_{T1} \to V_{OUT} \ge V_{IN} - V_{T1}$$

(2.18)

M2 is in the saturation region when

$$V_{SD2} \ge V_{SG2} - |V_{T2}| \to V_{DD} - V_{OUT} \ge V_{DD} - V_{IN} - |V_{T2}|$$

(2.19)

$\to V_{OUT} \le V_{IN} + |V_{T2}|$

Figure 2.7: Voltage transfer curve and circuit of the push-pull inverter [2].

#### CMOS Inverter Design Methodology

The inverter threshold voltage,  $V_{th}$  is defined as one of the most important parameters that characterize the steady-state input-output behavior of the CMOS inverter circuit. The CMOS inverter can, due to its inherent complementary push-pull operating mode, provide a full output voltage swing between 0 and  $V_{DD}$ , and therefore, the noise margins are relatively wide. Thus, the problem of designing a CMOS inverter can be reduced to setting the inverter threshold,  $V_{th}$ , to a desired voltage value [31]. Given the inverter threshold equation ratio as [31]

$$k_{R} = \frac{k_{n}}{k_{p}} = \left(\frac{V_{DD} + V_{TP} - V_{th}}{V_{th} - V_{TN}}\right)^{2}$$

(2.20)

Establishing that the switching threshold voltage of an *ideal* inverter is defined as

$$V_{th,ideal} = \frac{1}{2} \cdot V_{DD} \tag{2.21}$$

Since the operations of the n-channel MOS and the p-channel MOS transistors of the CMOS inverter are fully complementary, we can achieve completely symmetric input-output characteristics by setting the threshold voltages as  $V_T = V_{TN} = |V_{TP}|$ . The ratio  $k_R$  for a symmetrical inverter assumes that the gate oxide thickness,  $t_{ox}$ , and hence, the gate oxide capacitance,  $C_{OX}$ , have the same value for both n-channel MOS and p-channel MOS transistors. The unity-ratio condition for the ideal symmetric inverter requires that [31]

$$\frac{\left(\frac{W}{L}\right)_n}{\left(\frac{W}{L}\right)_p} = \frac{\mu_n}{\mu_p} \approx \frac{230cm^2/V \cdot s}{580cm^2/V \cdot s}$$

(2.22)

Hence,

$$\left(\frac{W}{L}\right)_p \approx 2.5 \left(\frac{W}{L}\right)_n \tag{2.23}$$

## 2.3.3 Differential Amplifier

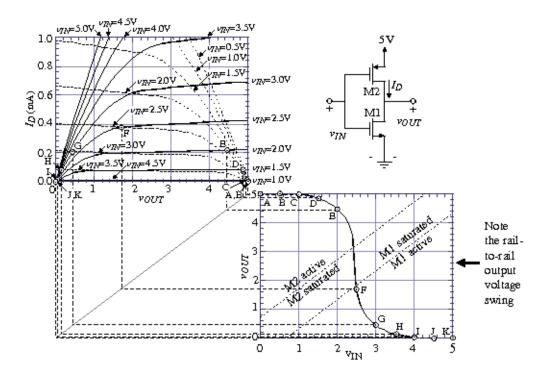

The differential amplifier is one of the more versatile circuits in analog circuit design. It is also very compatible with IC circuit technology and serves as the input stage to most operational amplifiers (op-amps). Figure 2.8 shows a schematic circuit for a differential amplifier [2].

Figure 2.8: Differential amplifier and its voltage-transfer curve [2].

#### Large-Signal Analysis

If we assume that the currents in the current mirror are identical, then  $I_{OUT}$  can be found by subtracting  $I_{D2}$  from  $I_{D1}$  for the n-channel differential amplifier of

Figure 2.8. Since  $I_{OUT}$  is a differential output current, the differential-in, differentialout transconductance is given as

$$g_{md} = \frac{\partial I_{OUT}}{\partial V_{ID}} (V_{ID} = 0) = \left(\frac{K_1' I_{SS} W_1}{L_1}\right)^{1/2}$$

(2.24)

Which is exactly equal to the transconductance of the common-source MOS transistor if  $I_D = I_{SS}/2$  [2].

The regions of operation for the transistors that conform the differential amplifier are shown on of Figure 2.8. Subscripts applied to the Figure and to the subsequent formulas mean the following: DS, for drain to source; GS, for gate to source; S, for source; IC, for input-common mode; ID, for input-differential mode; TN, for n-channel threshold; TP, for p-channel threshold; OUT, for the output node.

We note that the largest small-signal gain occurs when both M2 and M4 are saturated. M2 is saturated when